# **Design Rules**

© Digital Integrated Circuits<sup>2nd</sup>

#### **3D** Perspective

© Digital Integrated Circuits<sup>2nd</sup>

17 Manufacturing

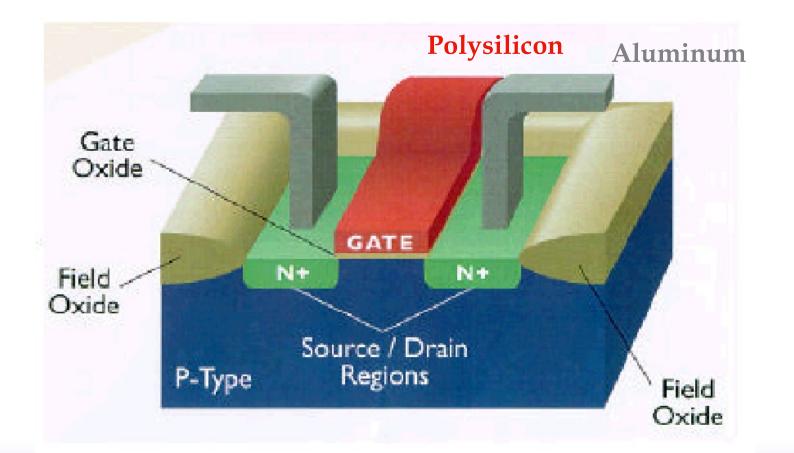

### **Design Rules**

- Interface between designer and process engineer

- Guidelines for constructing process masks

- □ Unit dimension: Minimum line width

- scalable design rules: lambda parameter

- absolute dimensions (micron rules)

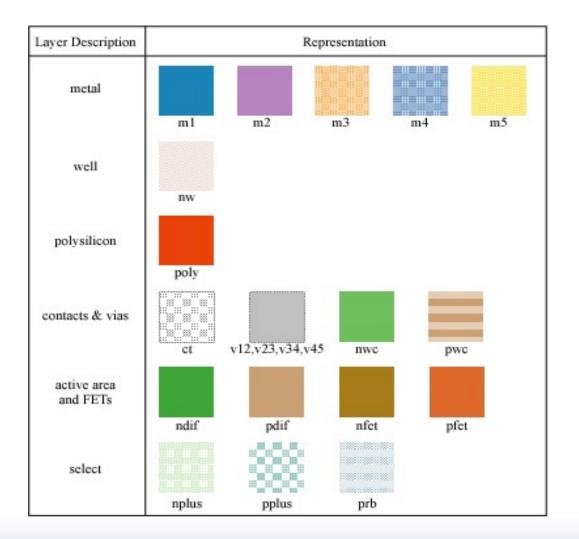

### **CMOS Process Layers**

| Layer                | Color   | Representation |

|----------------------|---------|----------------|

| Well (p,n)           | Yellow  |                |

| Active Area (n+,p+)  | Green   |                |

| Select (p+,n+)       | Green   | (              |

| Polysilicon          | Red     |                |

| Metal1               | Blue    |                |

| Metal2               | Magenta |                |

| Contact To Poly      | Black   |                |

| Contact To Diffusion | Black   |                |

| Via                  | Black   |                |

## Layers in 0.25 µm CMOS process

© Digital Integrated Circuits<sup>2nd</sup>