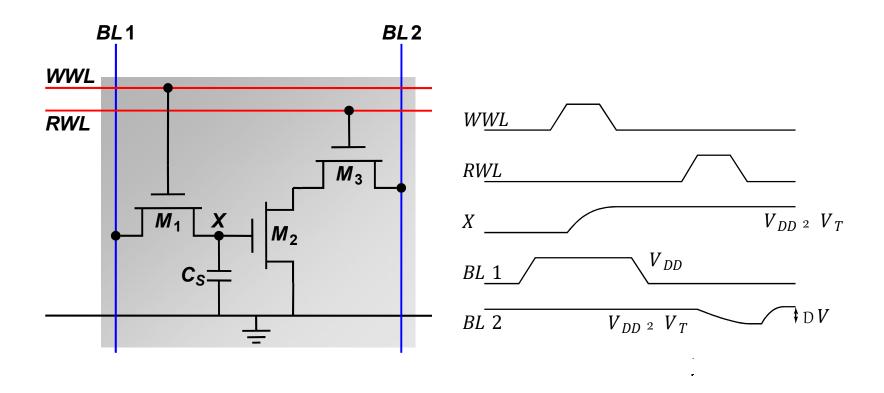

### 3-Transistor DRAM Cell

No constraints on device ratios Reads are non-destructive Value stored at node X when writing a "1" =  $V_{WWL}$ - $V_{Tn}$

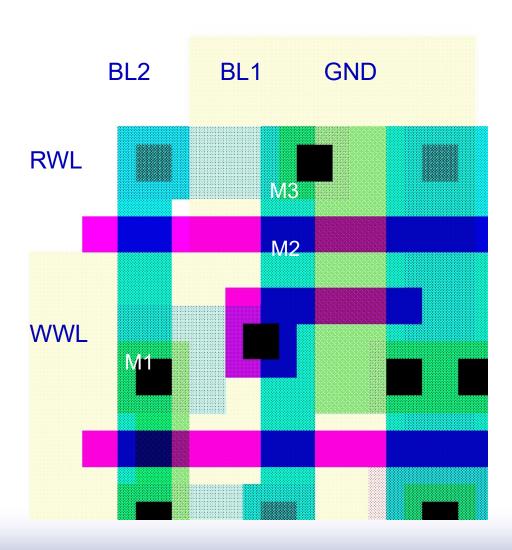

# 3T-DRAM — Layout

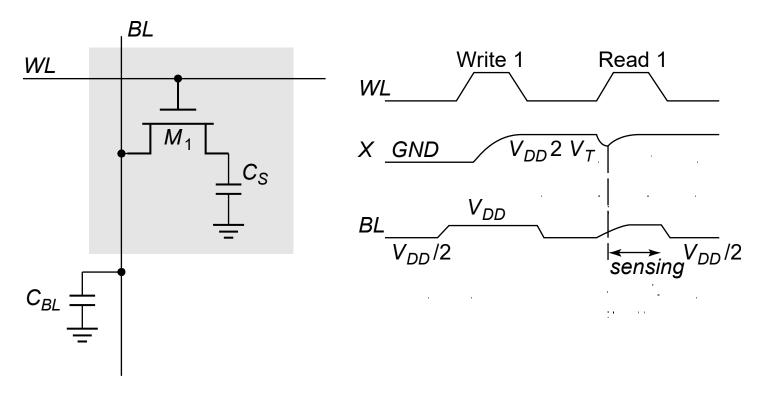

### 1-Transistor DRAM Cell

Write: C<sub>S</sub> is charged or discharged by asserting WL and BL.

Read: Charge redistribution takes places between bit line and storage capacitance

$$\Delta V = V_{BL} - V_{PRE} = V_{BIT} - V_{PRE} \frac{C_S}{C_S + C_{BL}}$$

Voltage swing is small; typically around 250 mV.

### DRAM Cell Observations

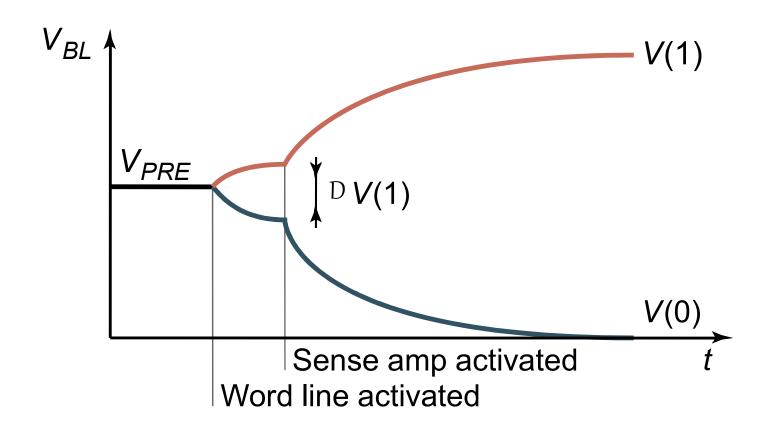

- □ 1T DRAM requires a sense amplifier for each bit line, due to charge redistribution read-out.

- □ DRAM memory cells are single ended in contrast to SRAM cells.

- □The read-out of the 1T DRAM cell is destructive; read and refresh operations are necessary for correct operation.

- ☐ Unlike 3T cell, 1T cell requires presence of an extra capacitance that must be explicitly included in the design.

- □ When writing a "1" into a DRAM cell, a threshold voltage is lost. This charge loss can be circumvented by bootstrapping the word lines to a higher value than  $V_{DD}$

# Sense Amp Operation

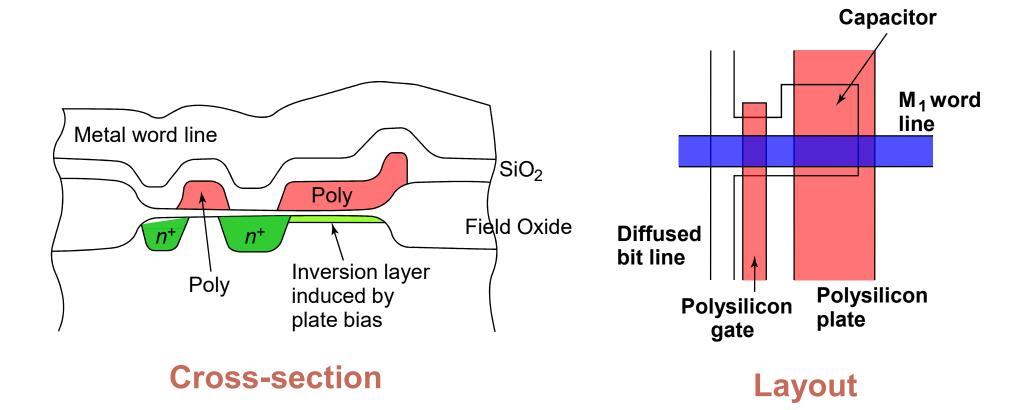

### 1-T DRAM Cell

Uses Polysilicon-Diffusion Capacitance

Expensive in Area

#### SEM of poly-diffusion capacitor 1T-DRAM

## Advanced 1T DRAM Cells

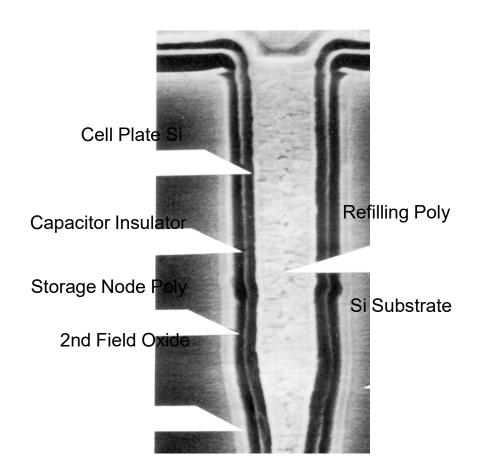

**Trench Cell**

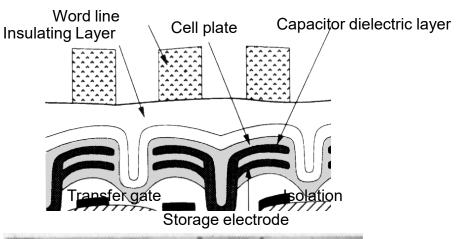

**Stacked-capacitor Cell**