#### **CMOS Process**

## A Modern CMOS Process

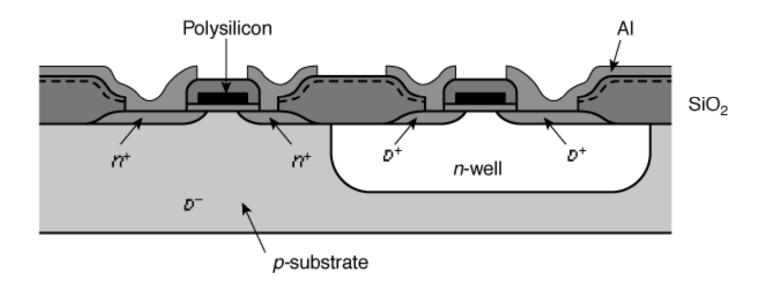

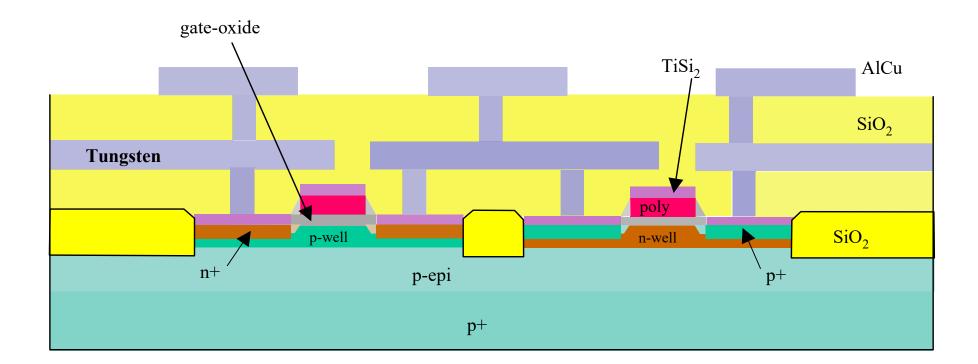

**Dual-Well Trench-Isolated CMOS Process**

© Digital Integrated Circuits<sup>2nd</sup>

<sup>3</sup> Manufacturing

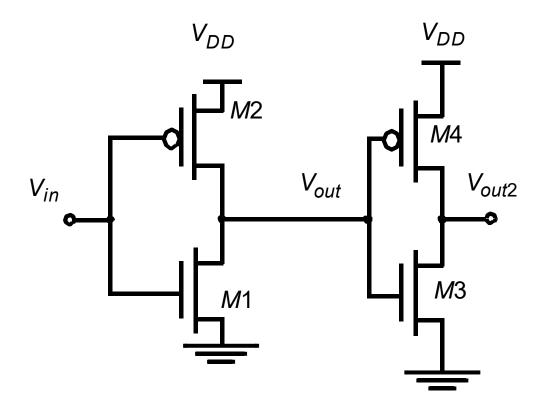

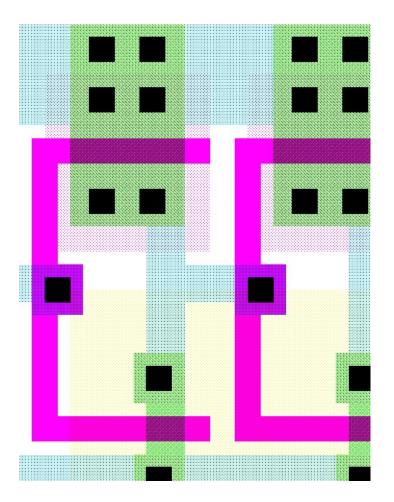

#### **Circuit Under Design**

# **Its Layout View**

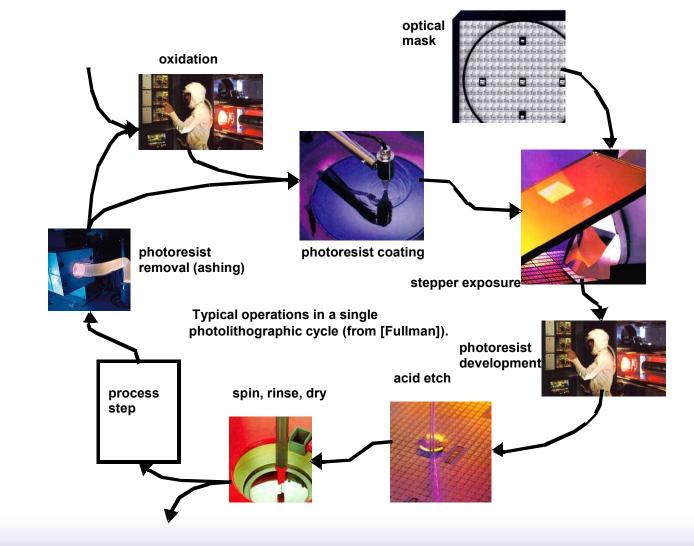

#### **The Manufacturing Process**

For a great tour through the IC manufacturing process and its different steps, check http://www.fullman.com/semiconductors/semiconductors.html

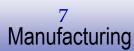

# **Photo-Lithographic Process**

# **Patterning of SiO2**

© Digital Integrated Circuits<sup>2nd</sup>

8 Manufacturing

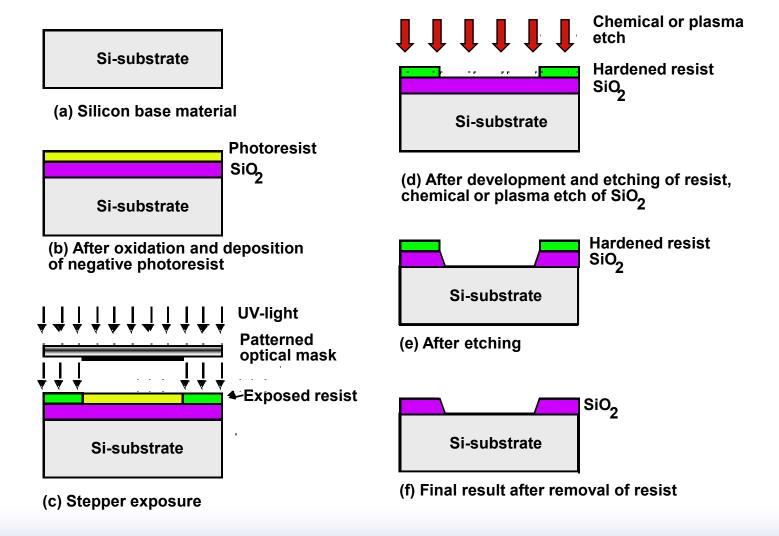

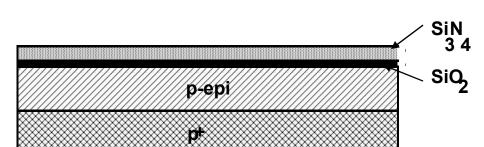

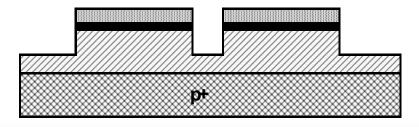

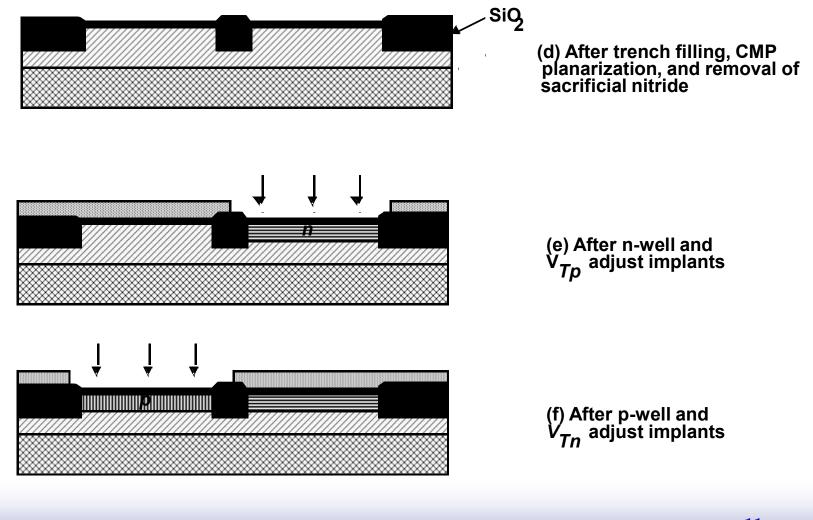

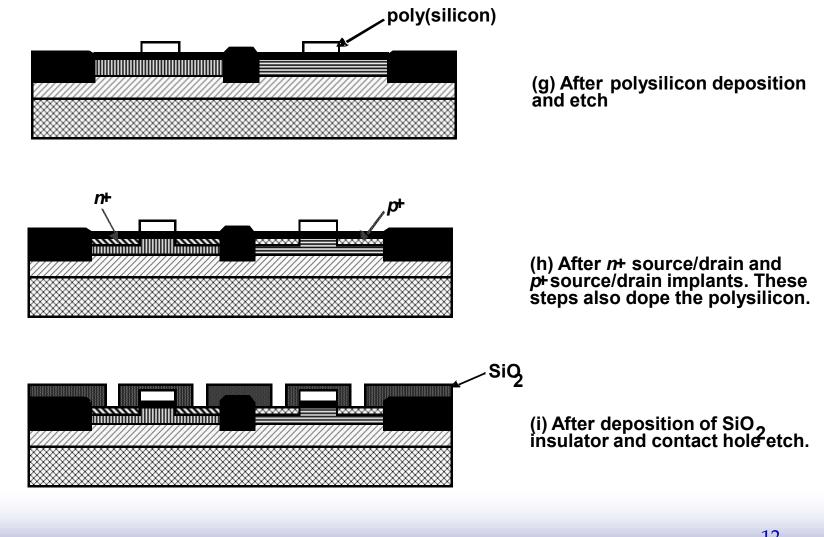

### **CMOS Process at a Glance**

(a) Base material: p+ substrate with p-epi layer

(b) After deposition of gate-oxide and sacrificial nitride (acts as a buffer layer)

(c) After plasma etch of insulating trenches using the inverse of the active area mask

10 Manufacturing

© Digital Integrated Circuits<sup>2nd</sup>

11 Manufacturing

© Digital Integrated Circuits<sup>2nd</sup>

12 Manufacturing

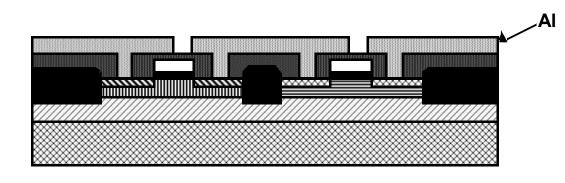

(j) After deposition and patterning of first Al layer.

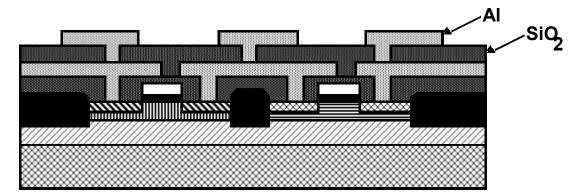

(k) After deposition of SiO <sub>2</sub> insulator, etching of via's, <sup>2</sup> deposition and patterning of second layer of Al.

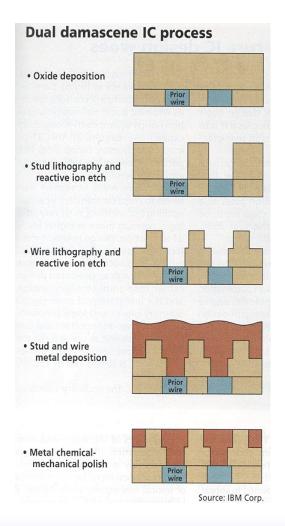

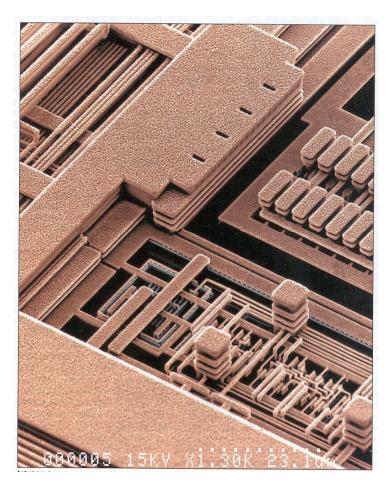

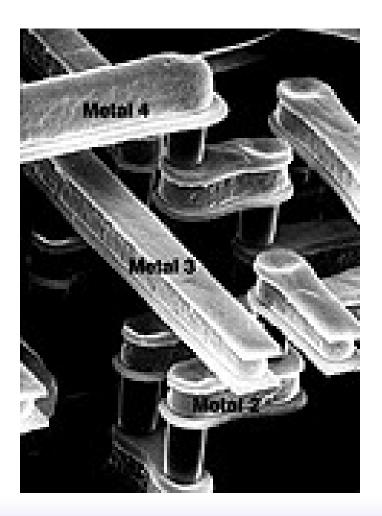

#### **Advanced Metallization**

### **Advanced Metallization**