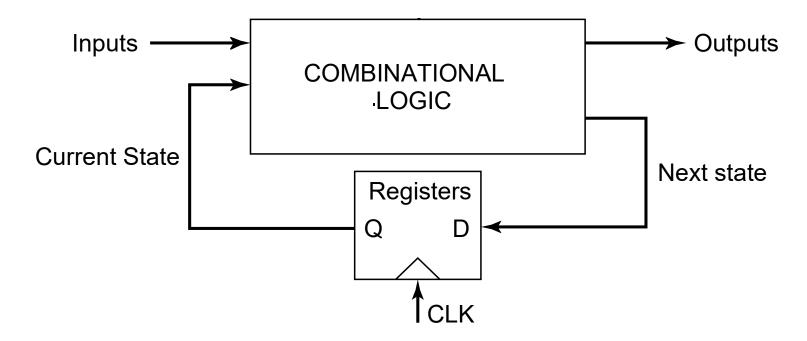

# Sequential Logic

#### 2 storage mechanisms

- positive feedback

- charge-based

## **Naming Conventions**

- □ In our text:

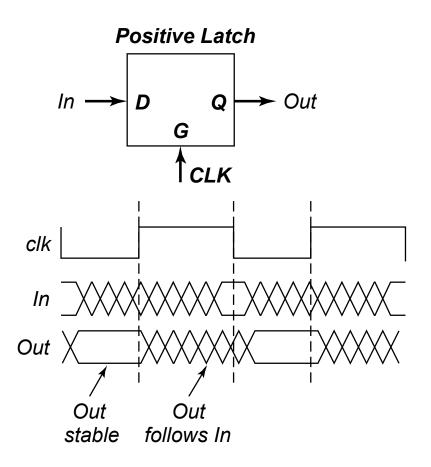

- a latch is level sensitive

- a register is edge-triggered

- There are many different naming conventions

- For instance, many books call edgetriggered elements flip-flops

- This leads to confusion however

### Latch versus Register

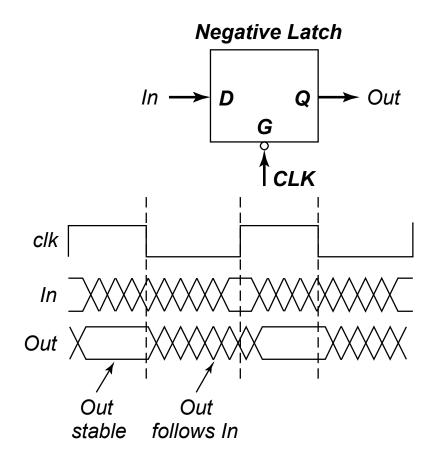

□ Latchstores data when clock is low

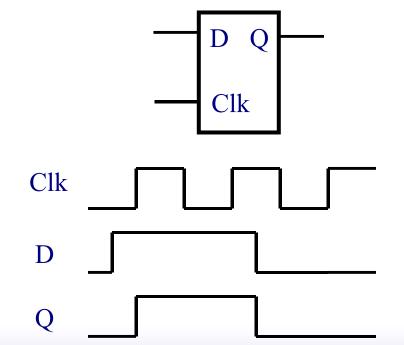

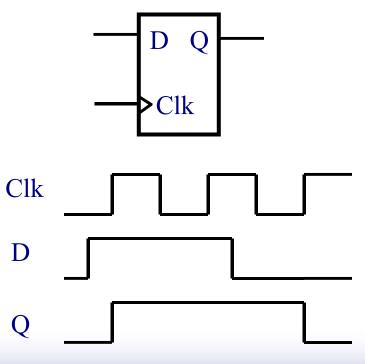

Registerstores data when clock rises

### Latches

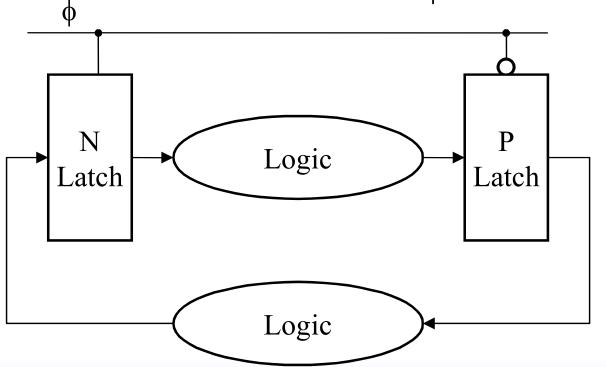

# Latch-Based Design

• N latch is transparent when  $\phi = 0$

• P latch is transparent when  $\phi = 1$

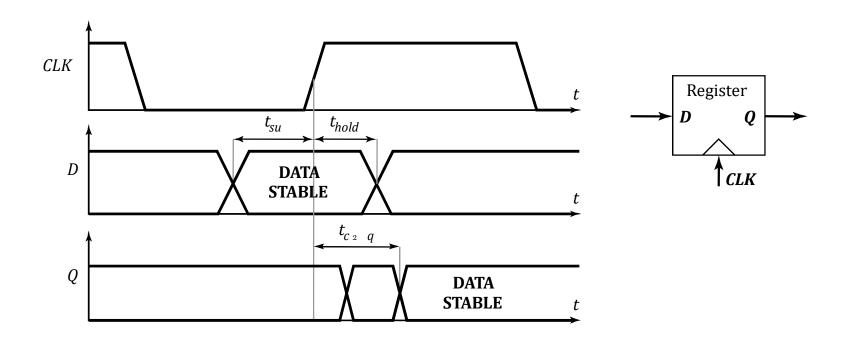

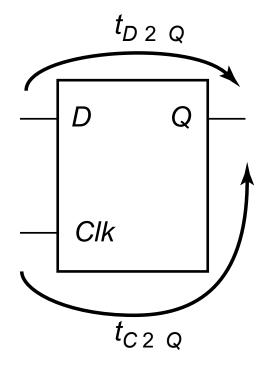

# **Timing Definitions**

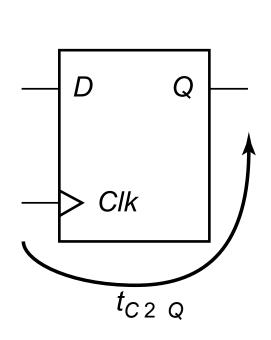

# **Characterizing Timing**

Register

Latch

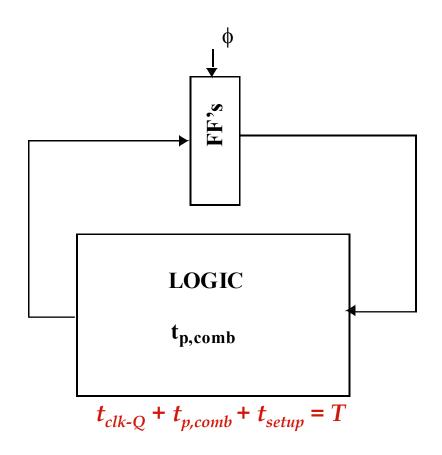

### Maximum Clock Frequency

Also:  $t_{cdreg} + t_{cdlogic} > t_{hold}$  $t_{cd}$ : contamination delay = minimum delay