# **Dynamic Logic**

© Digital Integrated Circuits<sup>2nd</sup>

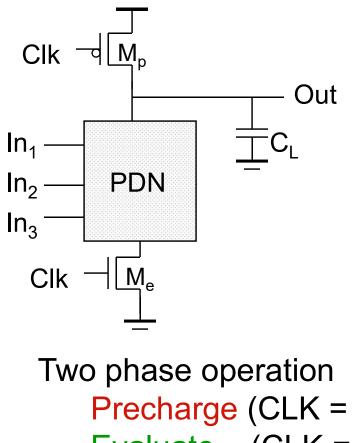

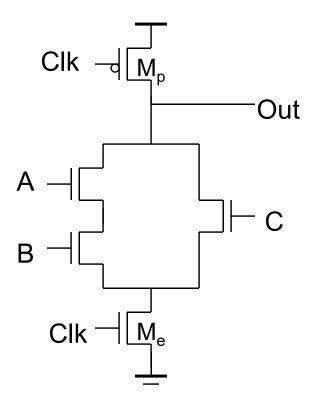

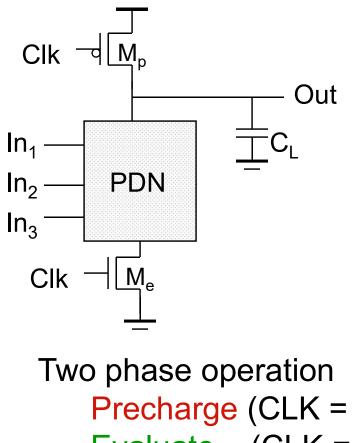

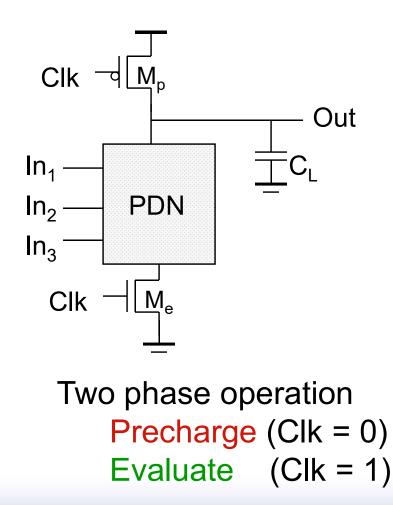

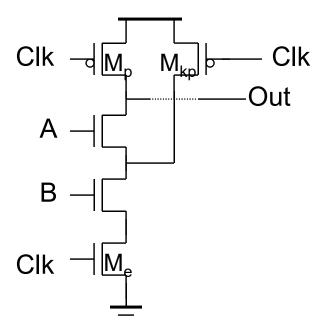

## **Dynamic CMOS**

□ In static circuits at every point in time (except when switching) the output is connected to either GND or  $V_{DD}$  via a low resistance path.

- fan-in of *n* requires 2n (n N-type + n P-type) devices

- Dynamic circuits rely on the temporary storage of signal values on the capacitance of high impedance nodes.

- requires on n + 2 (n+1 N-type + 1 P-type) transistors

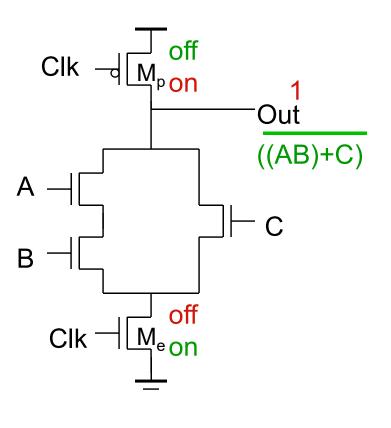

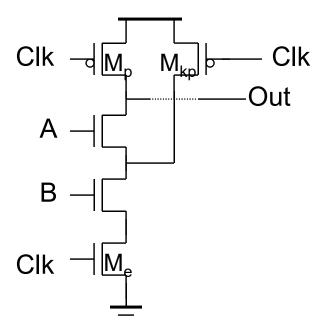

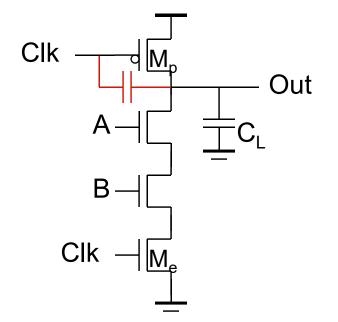

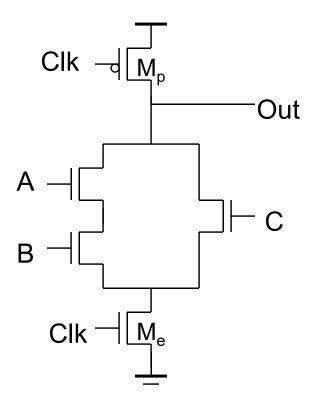

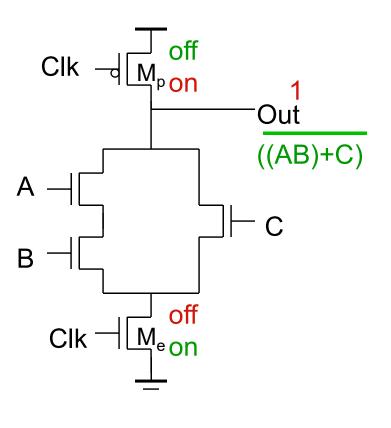

**Dynamic Gate**

Precharge (CLK = 0) Evaluate (CLK = 1)

© Digital Integrated Circuits<sup>2nd</sup>

**Dynamic Gate**

© Digital Integrated Circuits<sup>2nd</sup>

### **Conditions on Output**

- Once the output of a dynamic gate is discharged, it cannot be charged again until the next precharge operation.

- Inputs to the gate can make at most one transition during evaluation.

- Output can be in the high impedance state during and after evaluation (PDN off), state is stored on C<sub>L</sub>

## **Properties of Dynamic Gates**

□ Logic function is implemented by the PDN only

- number of transistors is N + 2 (versus 2N for static complementary CMOS)

- **□** Full swing outputs ( $V_{OL}$  = GND and  $V_{OH}$  =  $V_{DD}$ )

- Non-ratioed sizing of the devices does not affect the logic levels

- □ Faster switching speeds

- reduced load capacitance due to lower input capacitance (C<sub>in</sub>)

- reduced load capacitance due to smaller output loading (Cout)

- no I<sub>sc</sub>, so all the current provided by PDN goes into discharging C<sub>L</sub>

## **Properties of Dynamic Gates**

- Overall power dissipation usually higher than static CMOS

- no static current path ever exists between V<sub>DD</sub> and GND (including P<sub>sc</sub>)

- no glitching

- higher transition probabilities

- extra load on Clk

- $\square$  PDN starts to work as soon as the input signals exceed  $V_{Tn},$  so  $V_M,$   $V_{IH}$  and  $V_{IL}$  equal to  $V_{Tn}$

- low noise margin (NM<sub>L</sub>)

- Needs a precharge/evaluate clock

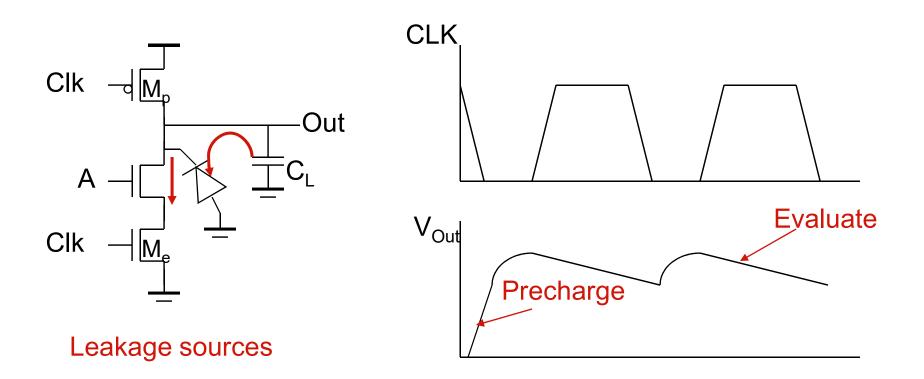

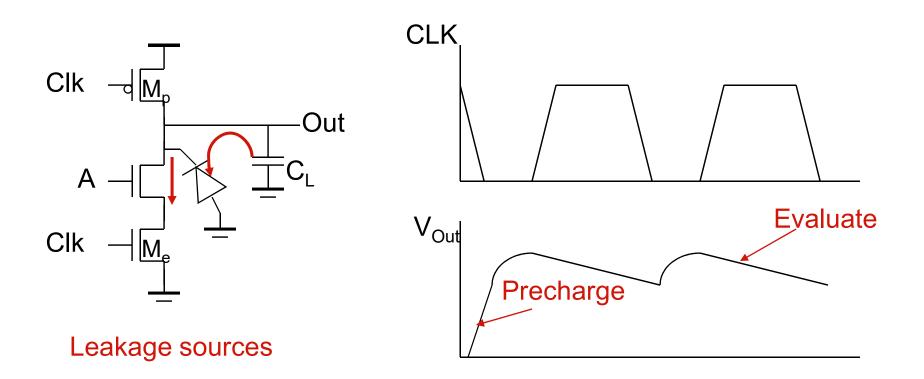

## Issues in Dynamic Design 1: Charge Leakage

Dominant component is subthreshold current

© Digital Integrated Circuits<sup>2nd</sup>

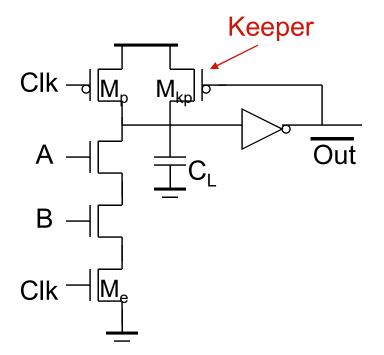

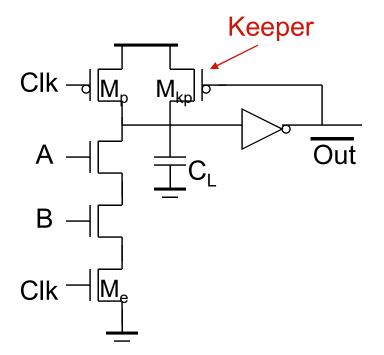

## **Solution to Charge Leakage**

Same approach as level restorer for pass-transistor logic

© Digital Integrated Circuits<sup>2nd</sup>

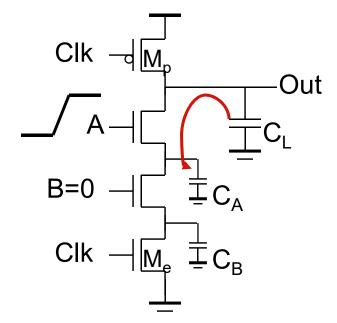

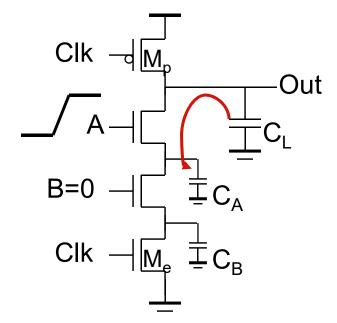

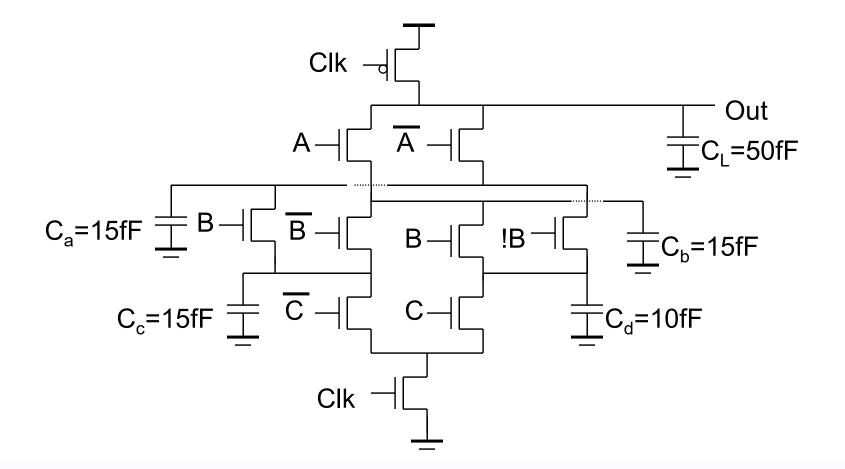

## Issues in Dynamic Design 2: Charge Sharing

Charge stored originally on  $C_L$  is redistributed (shared) over  $C_L$  and  $C_A$  leading to reduced robustness

#### **Charge Sharing Example**

© Digital Integrated Circuits<sup>2nd</sup>

**Charge Sharing**

$V_{DD}$ Clk Out  $C_L$  $M_a$ A X  $C_a$ B = 0 $M_b$  $C_b$ Clk  $M_e$

case 1) if  $\Delta V_{out} < V_{Tn}$

$$C_{L}V_{DD} = C_{L}V_{out}(t) + C_{a}(V_{DD} - V_{Tn}(V_{X}))$$

or

$$\Delta V_{out} = V_{out}(t) - V_{DD} = -\frac{C_{a}}{C_{L}}(V_{DD} - V_{Tn}(V_{X}))$$

case 2) if  $\Delta V_{out} > V_{Tn}$

$$\Delta \mathbf{V}_{out} = -\mathbf{V}_{DD} \left( \frac{\mathbf{C}_{a}}{\mathbf{C}_{a} + \mathbf{C}_{L}} \right)$$

99 Combinational Circuits

© Digital Integrated Circuits<sup>2nd</sup>

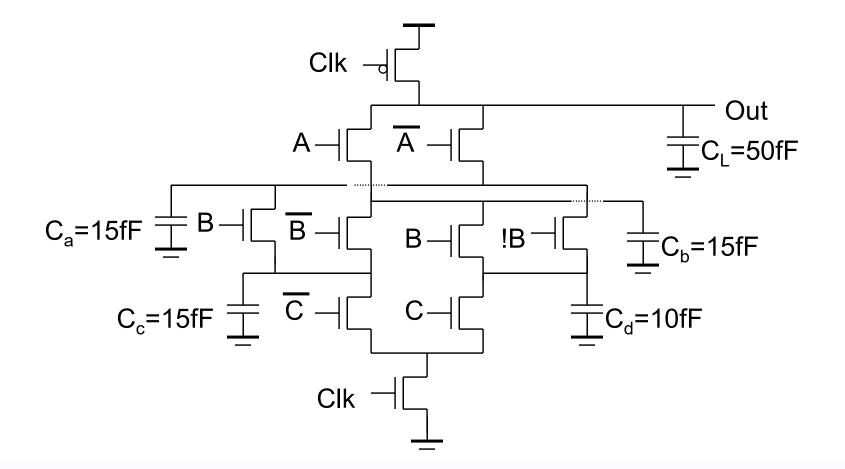

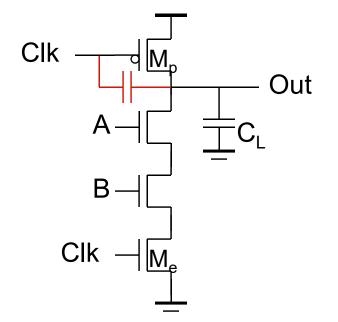

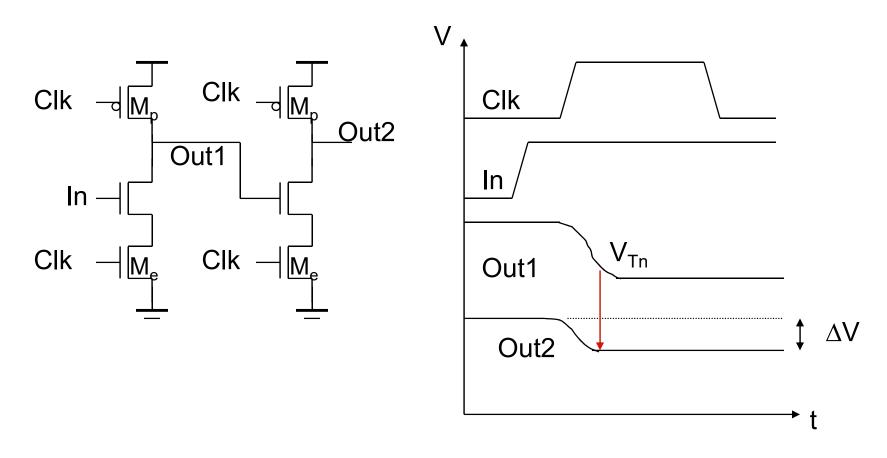

### **Solution to Charge Redistribution**

Precharge internal nodes using a clock-driven transistor (at the cost of increased area and power)

© Digital Integrated Circuits<sup>2nd</sup>

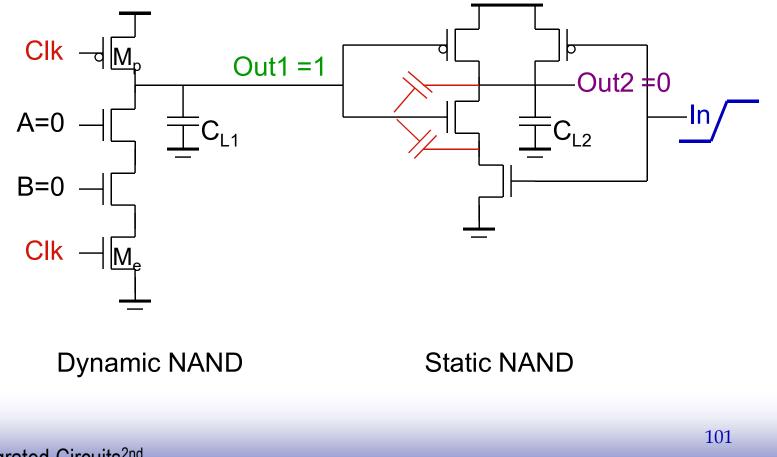

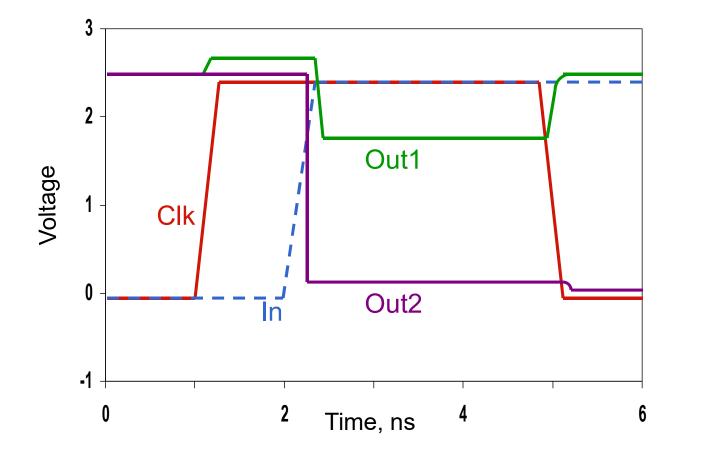

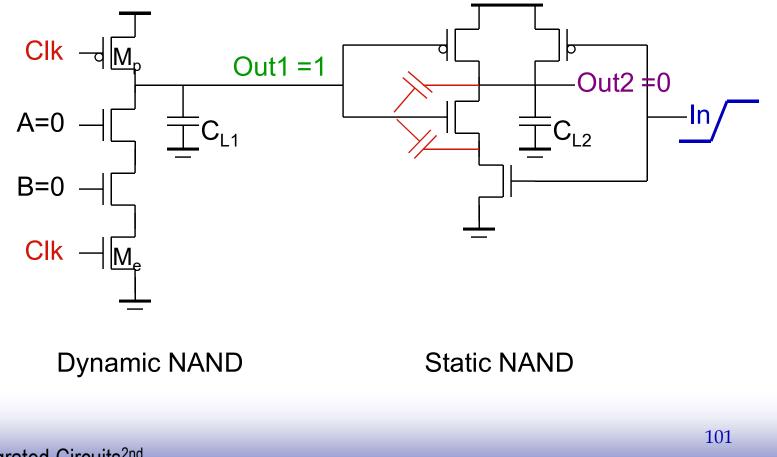

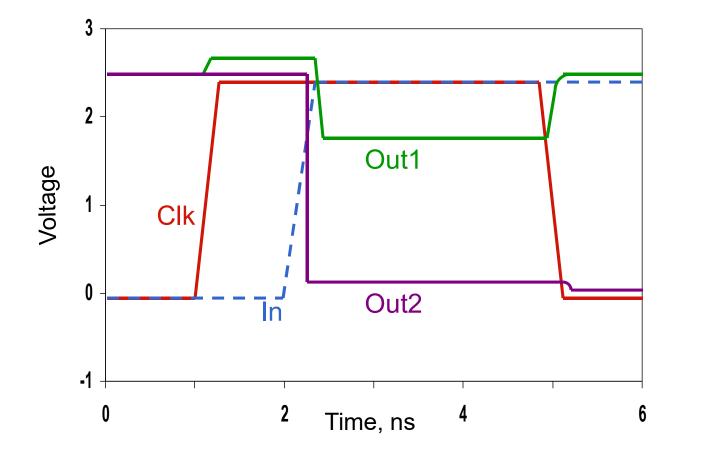

## Issues in Dynamic Design 3: Backgate Coupling

© Digital Integrated Circuits<sup>2nd</sup>

### **Backgate Coupling Effect**

102 Combinational Circuits

© Digital Integrated Circuits<sup>2nd</sup>

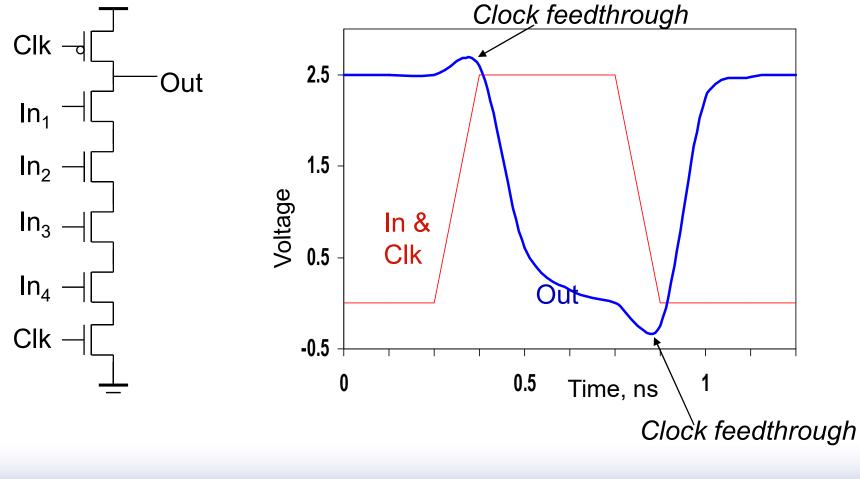

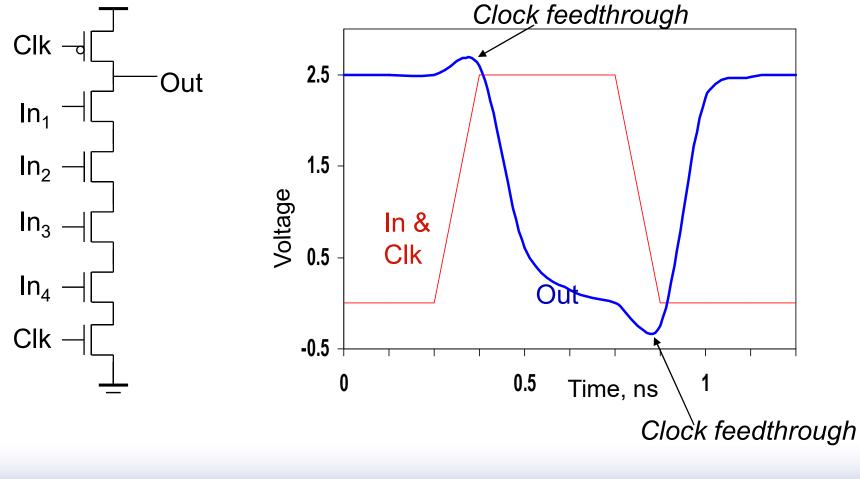

# Issues in Dynamic Design 4: Clock Feedthrough

Coupling between Out and Clk input of the precharge device due to the gate to drain capacitance. So voltage of Out can rise above  $V_{DD}$ . The fast rising (and falling edges) of the clock couple to Out.

#### **Clock Feedthrough**

© Digital Integrated Circuits<sup>2nd</sup>

Capacitive coupling

Substrate coupling

Minority charge injection

Supply noise (ground bounce)

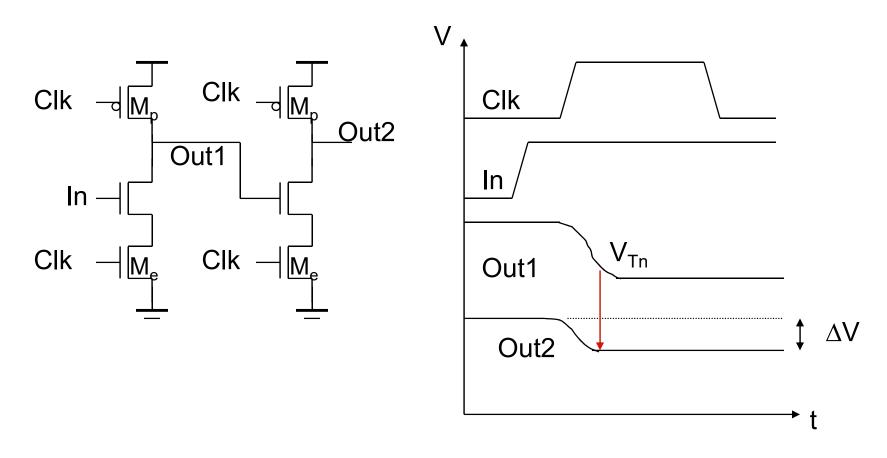

#### **Cascading Dynamic Gates**

Only  $0 \rightarrow 1$  transitions allowed at inputs!

© Digital Integrated Circuits<sup>2nd</sup>

# **Dynamic Logic**

© Digital Integrated Circuits<sup>2nd</sup>

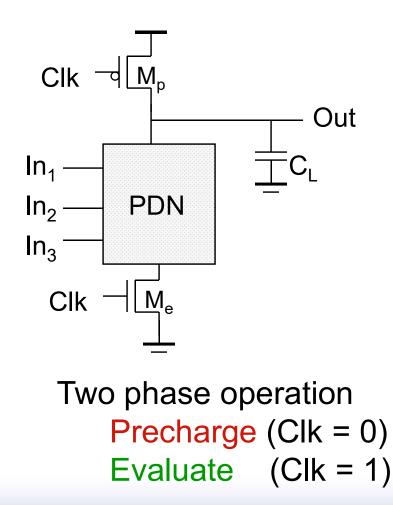

## **Dynamic CMOS**

□ In static circuits at every point in time (except when switching) the output is connected to either GND or  $V_{DD}$  via a low resistance path.

- fan-in of *n* requires 2n (n N-type + n P-type) devices

- Dynamic circuits rely on the temporary storage of signal values on the capacitance of high impedance nodes.

- requires on n + 2 (n+1 N-type + 1 P-type) transistors

**Dynamic Gate**

Precharge (CLK = 0) Evaluate (CLK = 1)

© Digital Integrated Circuits<sup>2nd</sup>

**Dynamic Gate**

© Digital Integrated Circuits<sup>2nd</sup>

### **Conditions on Output**

- Once the output of a dynamic gate is discharged, it cannot be charged again until the next precharge operation.

- Inputs to the gate can make at most one transition during evaluation.

- Output can be in the high impedance state during and after evaluation (PDN off), state is stored on C<sub>L</sub>

## **Properties of Dynamic Gates**

□ Logic function is implemented by the PDN only

- number of transistors is N + 2 (versus 2N for static complementary CMOS)

- **□** Full swing outputs ( $V_{OL}$  = GND and  $V_{OH}$  =  $V_{DD}$ )

- Non-ratioed sizing of the devices does not affect the logic levels

- □ Faster switching speeds

- reduced load capacitance due to lower input capacitance (C<sub>in</sub>)

- reduced load capacitance due to smaller output loading (Cout)

- no I<sub>sc</sub>, so all the current provided by PDN goes into discharging C<sub>L</sub>

## **Properties of Dynamic Gates**

- Overall power dissipation usually higher than static CMOS

- no static current path ever exists between V<sub>DD</sub> and GND (including P<sub>sc</sub>)

- no glitching

- higher transition probabilities

- extra load on Clk

- $\square$  PDN starts to work as soon as the input signals exceed  $V_{Tn},$  so  $V_M,$   $V_{IH}$  and  $V_{IL}$  equal to  $V_{Tn}$

- low noise margin (NM<sub>L</sub>)

- Needs a precharge/evaluate clock

## Issues in Dynamic Design 1: Charge Leakage

Dominant component is subthreshold current

© Digital Integrated Circuits<sup>2nd</sup>

## **Solution to Charge Leakage**

Same approach as level restorer for pass-transistor logic

© Digital Integrated Circuits<sup>2nd</sup>

## Issues in Dynamic Design 2: Charge Sharing

Charge stored originally on  $C_L$  is redistributed (shared) over  $C_L$  and  $C_A$  leading to reduced robustness

#### **Charge Sharing Example**

© Digital Integrated Circuits<sup>2nd</sup>

**Charge Sharing**

$V_{DD}$ Clk Out  $C_L$  $M_a$ A X  $C_a$ B = 0 $M_b$  $C_b$ Clk  $M_e$

case 1) if  $\Delta V_{out} < V_{Tn}$

$$C_{L}V_{DD} = C_{L}V_{out}(t) + C_{a}(V_{DD} - V_{Tn}(V_{X}))$$

or

$$\Delta V_{out} = V_{out}(t) - V_{DD} = -\frac{C_{a}}{C_{L}}(V_{DD} - V_{Tn}(V_{X}))$$

case 2) if  $\Delta V_{out} > V_{Tn}$

$$\Delta \mathbf{V}_{out} = -\mathbf{V}_{DD} \left( \frac{\mathbf{C}_{a}}{\mathbf{C}_{a} + \mathbf{C}_{L}} \right)$$

99 Combinational Circuits

© Digital Integrated Circuits<sup>2nd</sup>

### **Solution to Charge Redistribution**

Precharge internal nodes using a clock-driven transistor (at the cost of increased area and power)

© Digital Integrated Circuits<sup>2nd</sup>

## Issues in Dynamic Design 3: Backgate Coupling

© Digital Integrated Circuits<sup>2nd</sup>

### **Backgate Coupling Effect**

102 Combinational Circuits

© Digital Integrated Circuits<sup>2nd</sup>

# Issues in Dynamic Design 4: Clock Feedthrough

Coupling between Out and Clk input of the precharge device due to the gate to drain capacitance. So voltage of Out can rise above  $V_{DD}$ . The fast rising (and falling edges) of the clock couple to Out.

#### **Clock Feedthrough**

© Digital Integrated Circuits<sup>2nd</sup>

Capacitive coupling

Substrate coupling

Minority charge injection

Supply noise (ground bounce)

#### **Cascading Dynamic Gates**

Only  $0 \rightarrow 1$  transitions allowed at inputs!

© Digital Integrated Circuits<sup>2nd</sup>