## Pass-Transistor Logic

© Digital Integrated Circuits<sup>2nd</sup>

## **Pass-Transistor Logic**

- N transistors

- No static consumption

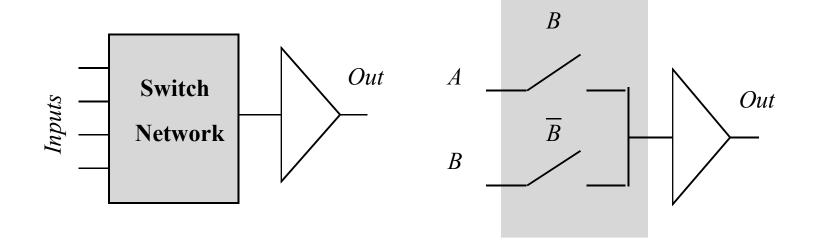

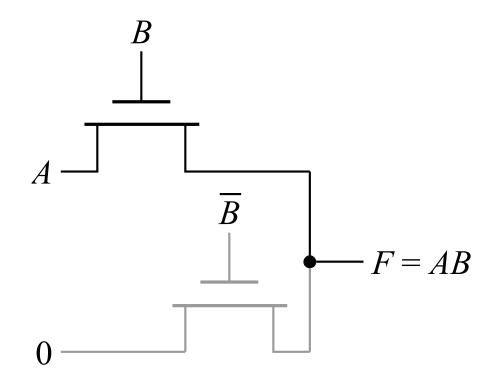

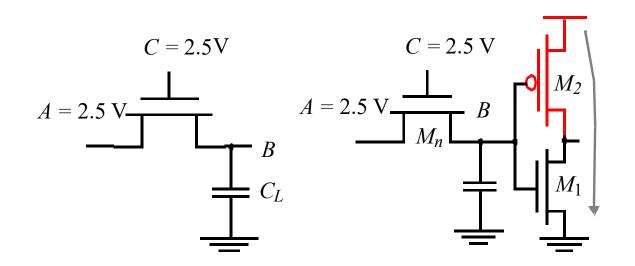

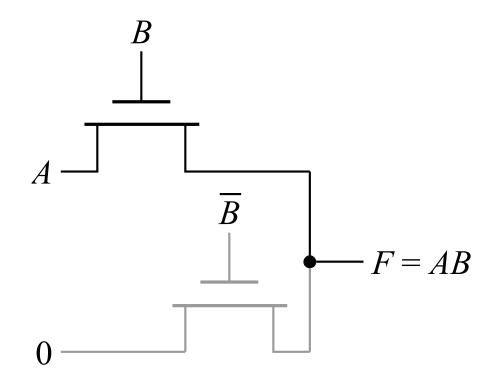

## **Example: AND Gate**

© Digital Integrated Circuits<sup>2nd</sup>

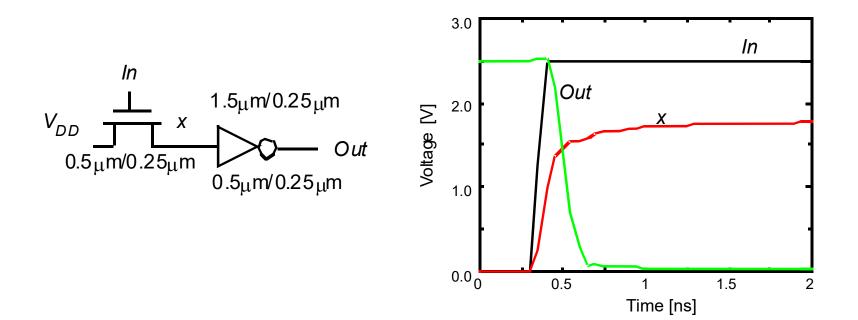

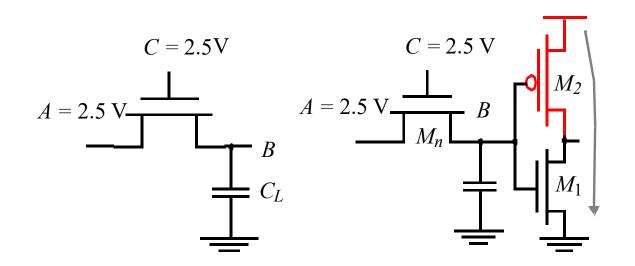

## **NMOS-Only Logic**

© Digital Integrated Circuits<sup>2nd</sup>

## **NMOS-only Switch**

$V_B$  does not pull up to 2.5V, but 2.5V -  $V_{TN}$

Threshold voltage loss causes static power consumption

NMOS has higher threshold than PMOS (body effect)

© Digital Integrated Circuits<sup>2nd</sup>

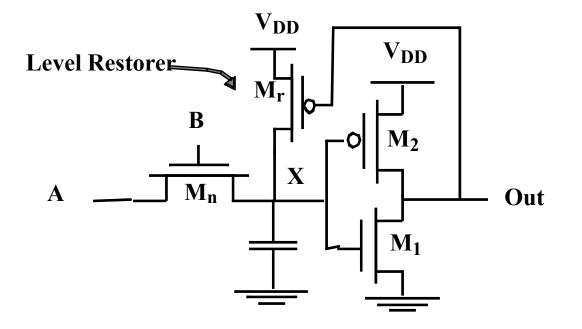

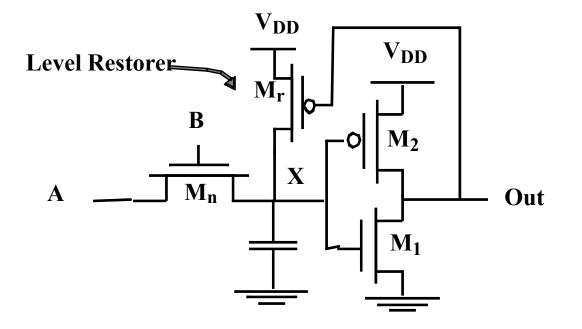

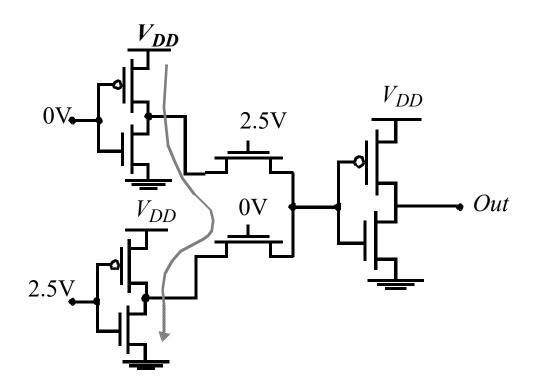

## NMOS Only Logic: Level Restoring Transistor

- Advantage: Full Swing

- Restorer adds capacitance, takes away pull down current at X

- Ratio problem

© Digital Integrated Circuits<sup>2nd</sup>

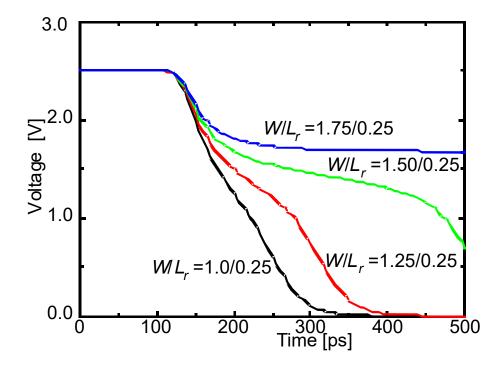

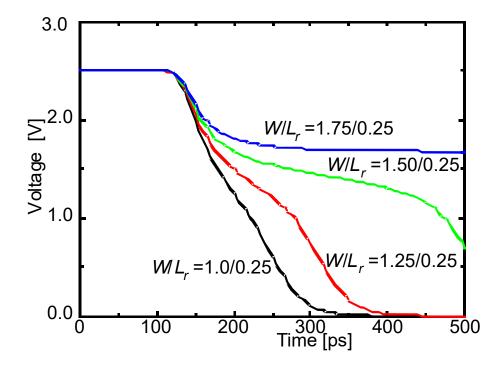

## **Restorer Sizing**

Upper limit on restorer size

Pass-transistor pull-down can have several transistors in stack

© Digital Integrated Circuits<sup>2nd</sup>

# Solution 2: Single Transistor Pass Gate with $V_T=0$

WATCH OUT FOR LEAKAGE CURRENTS

79 Combinational Circuits

© Digital Integrated Circuits<sup>2nd</sup>

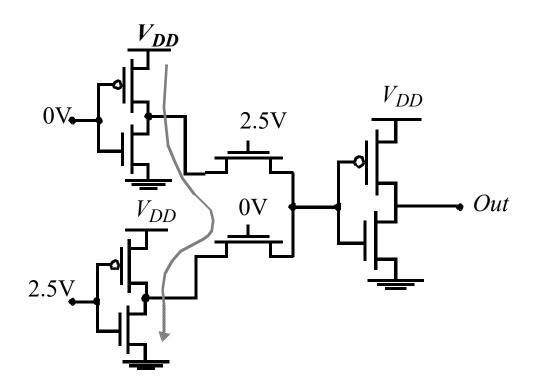

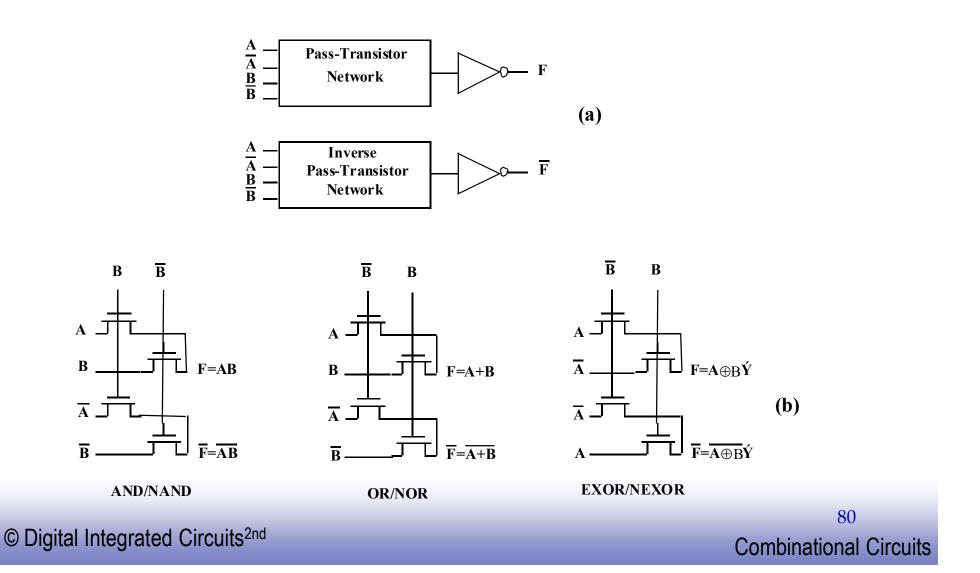

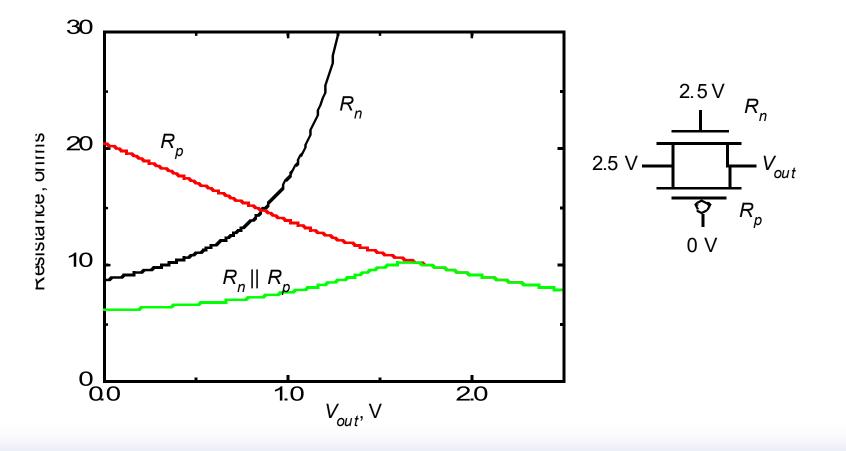

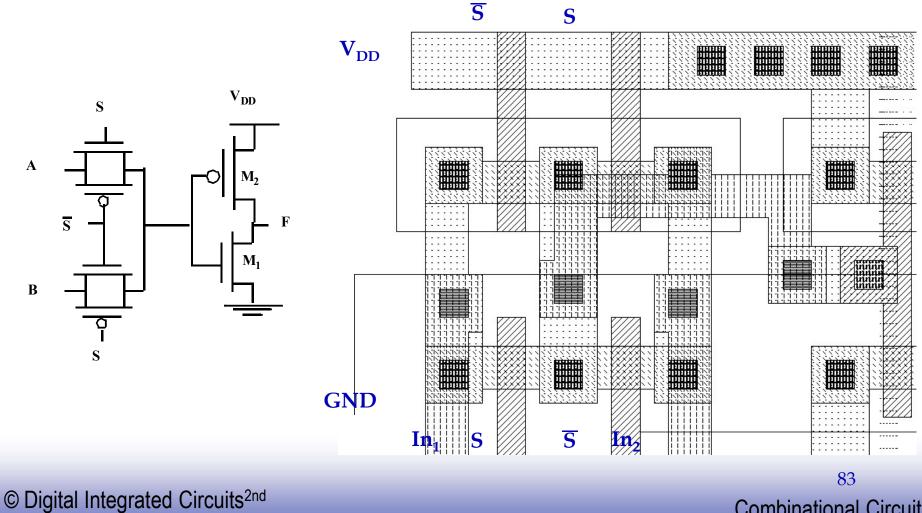

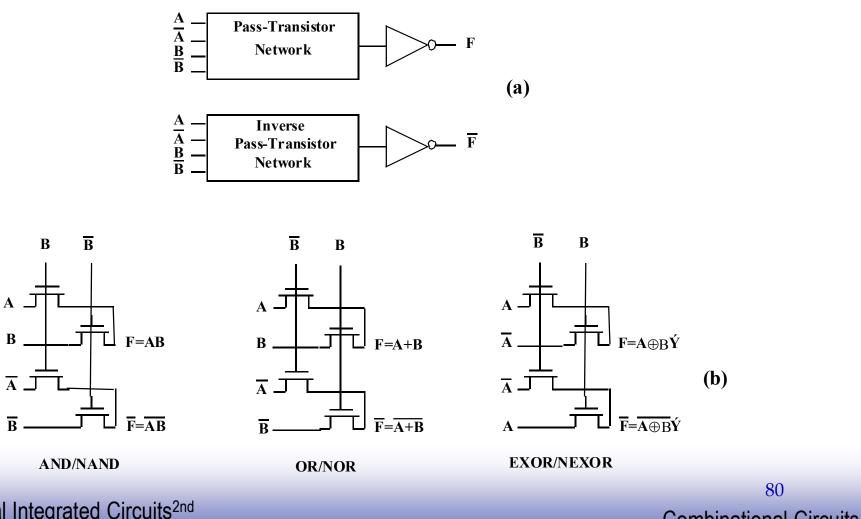

#### **Complementary Pass Transistor Logic**

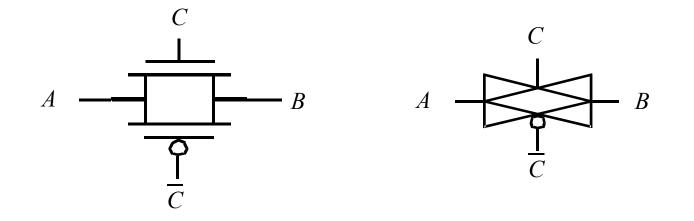

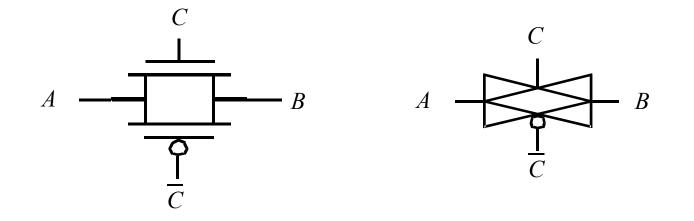

## **Solution 3: Transmission Gate**

© Digital Integrated Circuits<sup>2nd</sup>

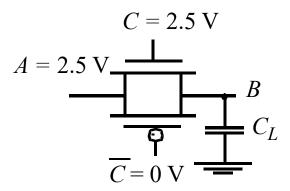

#### **Resistance of Transmission Gate**

© Digital Integrated Circuits<sup>2nd</sup>

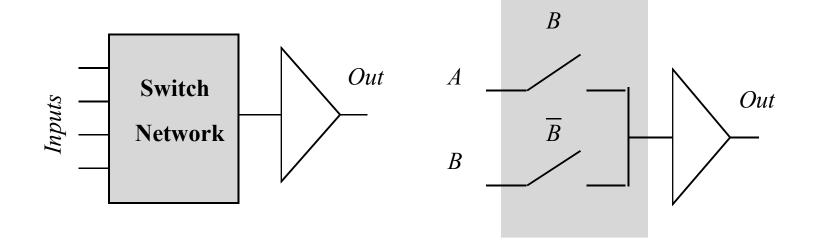

#### **Pass-Transistor Based Multiplexer**

## **Transmission Gate XOR**

© Digital Integrated Circuits<sup>2nd</sup>

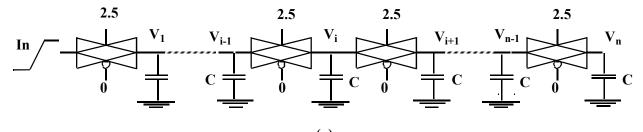

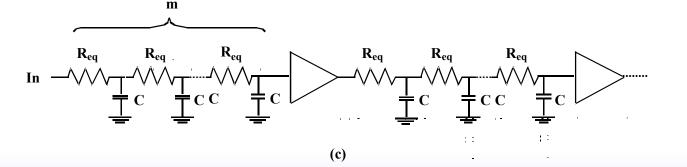

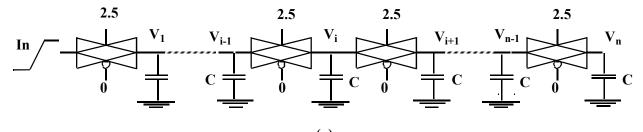

#### **Delay in Transmission Gate Networks**

**(a)**

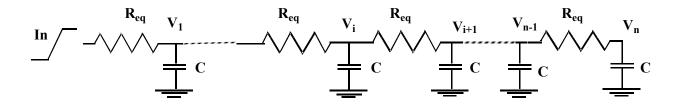

**(b)**

© Digital Integrated Circuits<sup>2nd</sup>

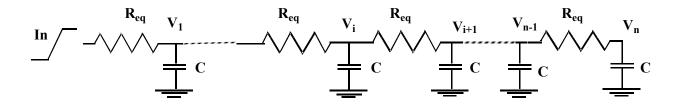

## **Delay Optimization**

Delay of RC chain

$$t_p = 0.69 \sum_{k=0}^{n} CR_{eq}k = 0.69CR_{eq}\frac{n(n+1)}{2}$$

## • Delay of Buffered Chain $t_p = 0.69 \left\lfloor \frac{n}{m} CR_{eq} \frac{m(m+1)}{2} \right\rfloor + \left( \frac{n}{m} - 1 \right) t_{buf}$ $= 0.69 \left[ CR_{eq} \frac{n(m+1)}{2} \right] + \left( \frac{n}{m} - 1 \right) t_{buf}$

$$m_{opt} = 1.7 \sqrt{\frac{t_{pbuf}}{CR_{eq}}}$$

© Digital Integrated Circuits<sup>2nd</sup>

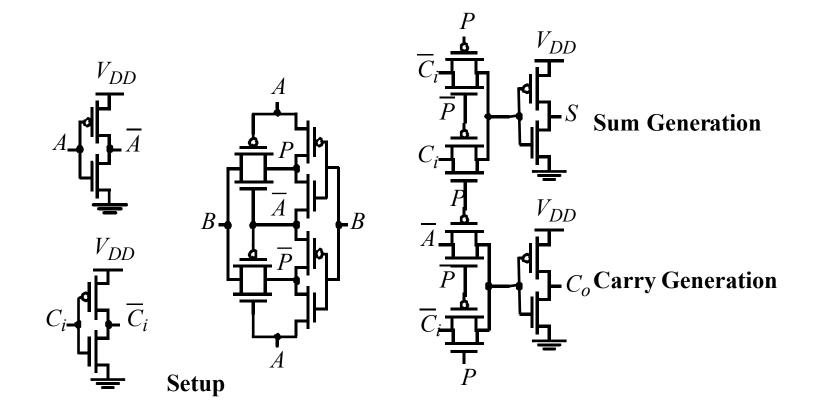

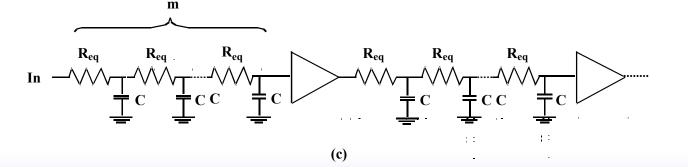

#### **Transmission Gate Full Adder**

Similar delays for sum and carry

© Digital Integrated Circuits<sup>2nd</sup>

## Pass-Transistor Logic

© Digital Integrated Circuits<sup>2nd</sup>

## **Pass-Transistor Logic**

- N transistors

- No static consumption

## **Example: AND Gate**

© Digital Integrated Circuits<sup>2nd</sup>

## **NMOS-Only Logic**

© Digital Integrated Circuits<sup>2nd</sup>

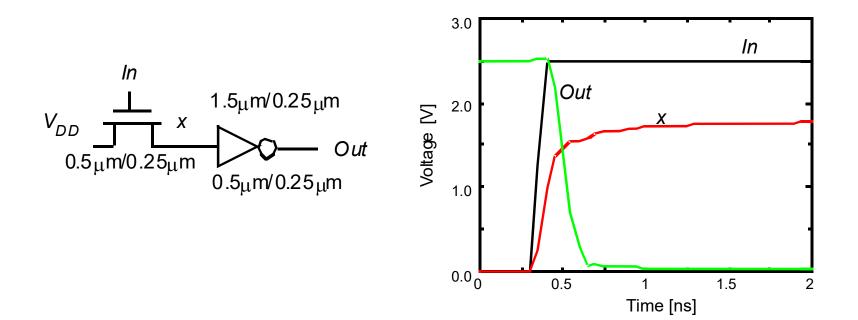

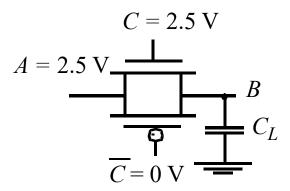

## **NMOS-only Switch**

$V_B$  does not pull up to 2.5V, but 2.5V -  $V_{TN}$

Threshold voltage loss causes static power consumption

NMOS has higher threshold than PMOS (body effect)

© Digital Integrated Circuits<sup>2nd</sup>

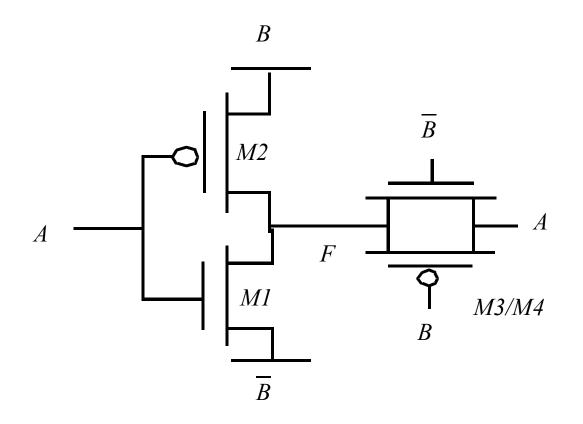

## NMOS Only Logic: Level Restoring Transistor

- Advantage: Full Swing

- Restorer adds capacitance, takes away pull down current at X

- Ratio problem

© Digital Integrated Circuits<sup>2nd</sup>

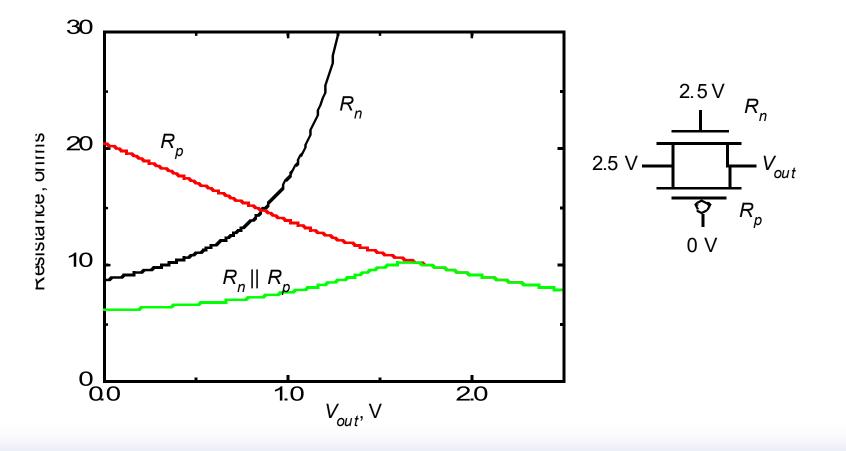

## **Restorer Sizing**

Upper limit on restorer size

Pass-transistor pull-down can have several transistors in stack

© Digital Integrated Circuits<sup>2nd</sup>

# Solution 2: Single Transistor Pass Gate with $V_T=0$

WATCH OUT FOR LEAKAGE CURRENTS

79 Combinational Circuits

© Digital Integrated Circuits<sup>2nd</sup>

#### **Complementary Pass Transistor Logic**

© Digital Integrated Circuits<sup>2nd</sup>

## **Solution 3: Transmission Gate**

© Digital Integrated Circuits<sup>2nd</sup>

#### **Resistance of Transmission Gate**

© Digital Integrated Circuits<sup>2nd</sup>

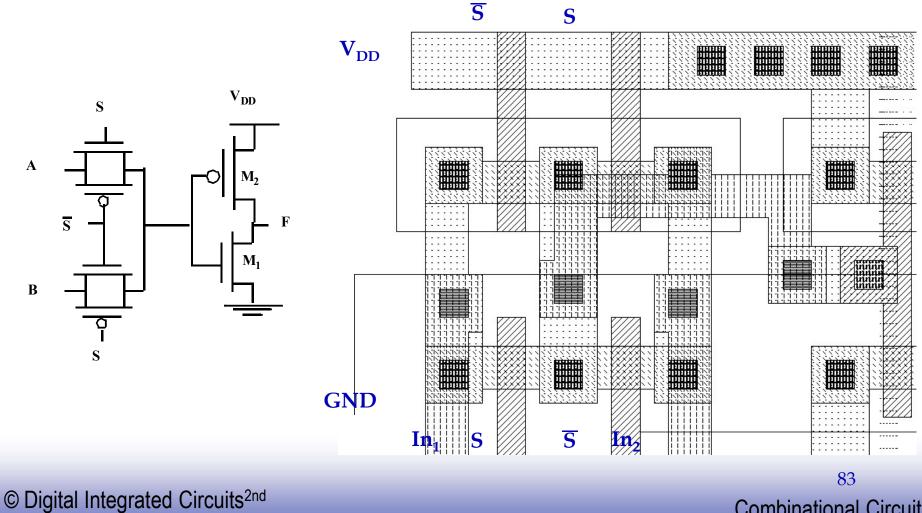

#### **Pass-Transistor Based Multiplexer**

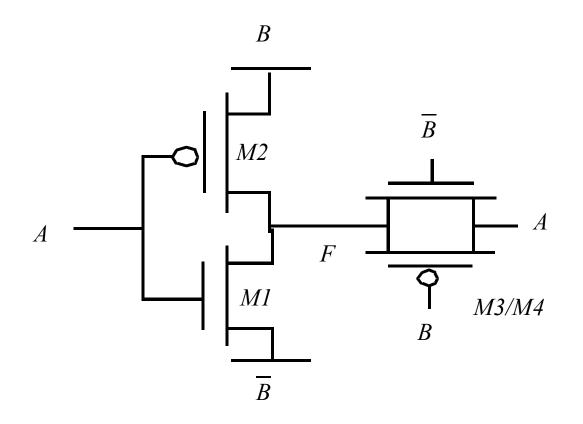

## **Transmission Gate XOR**

© Digital Integrated Circuits<sup>2nd</sup>

#### **Delay in Transmission Gate Networks**

**(a)**

**(b)**

© Digital Integrated Circuits<sup>2nd</sup>

## **Delay Optimization**

Delay of RC chain

$$t_p = 0.69 \sum_{k=0}^{n} CR_{eq}k = 0.69CR_{eq}\frac{n(n+1)}{2}$$

## • Delay of Buffered Chain $t_p = 0.69 \left\lfloor \frac{n}{m} CR_{eq} \frac{m(m+1)}{2} \right\rfloor + \left( \frac{n}{m} - 1 \right) t_{buf}$ $= 0.69 \left[ CR_{eq} \frac{n(m+1)}{2} \right] + \left( \frac{n}{m} - 1 \right) t_{buf}$

$$m_{opt} = 1.7 \sqrt{\frac{t_{pbuf}}{CR_{eq}}}$$

© Digital Integrated Circuits<sup>2nd</sup>

#### **Transmission Gate Full Adder**

Similar delays for sum and carry

© Digital Integrated Circuits<sup>2nd</sup>