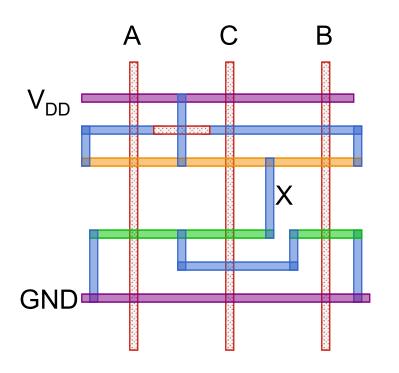

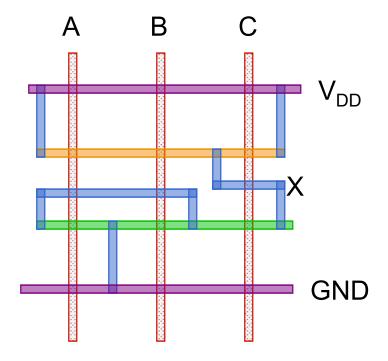

#### Stick Diagrams

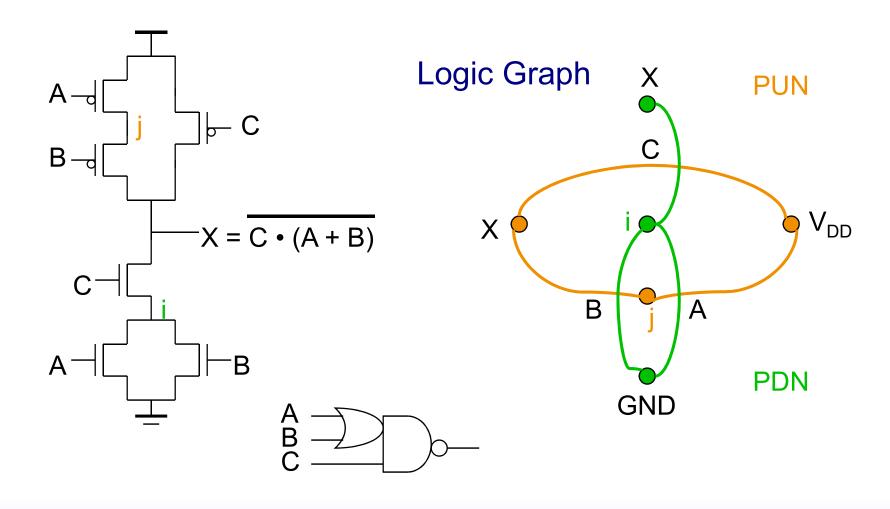

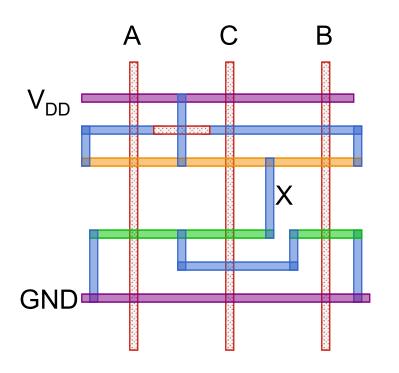

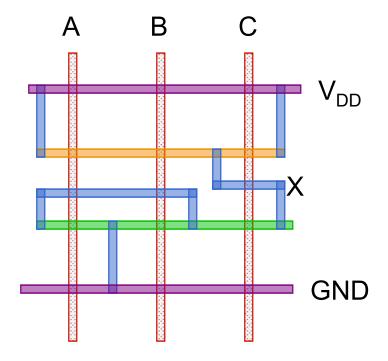

## Two Versions of C • (A + B)

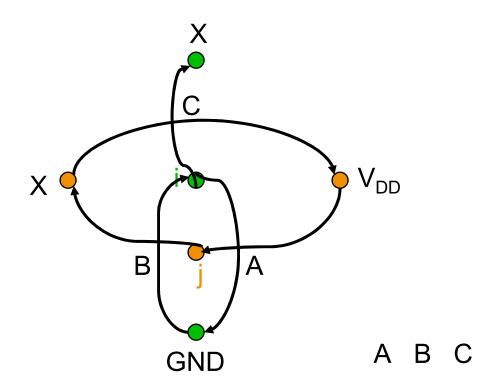

#### Consistent Euler Path

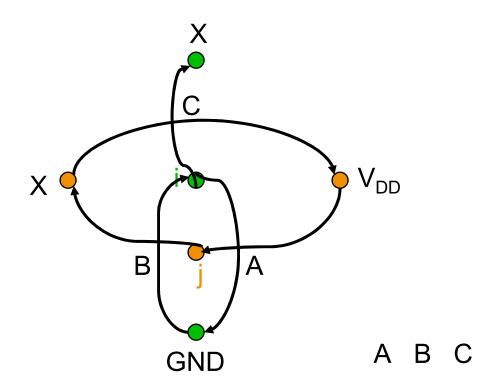

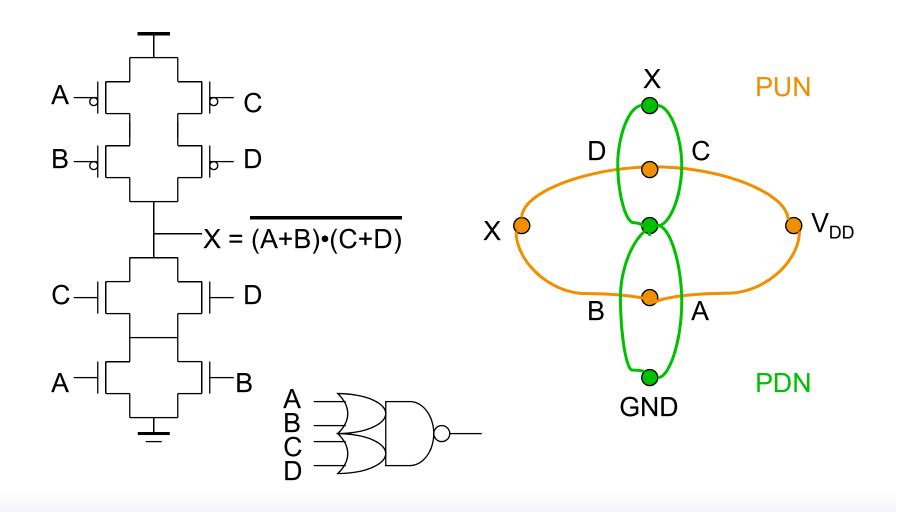

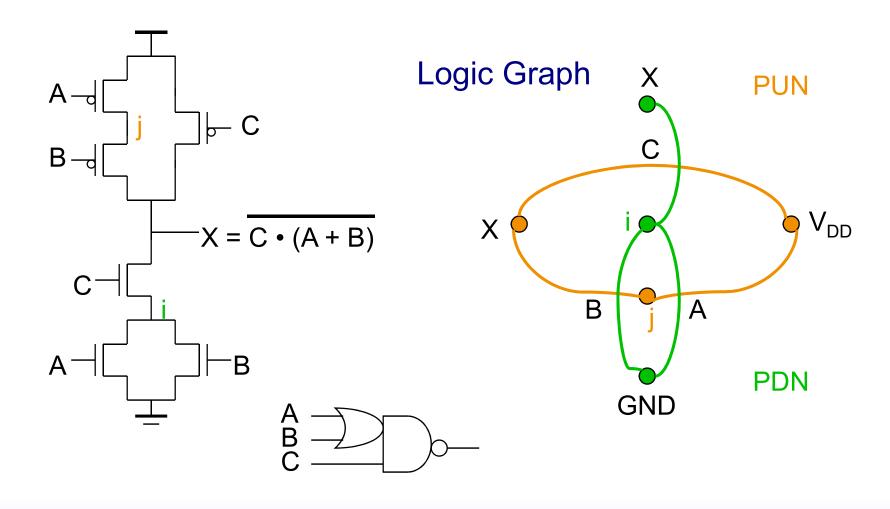

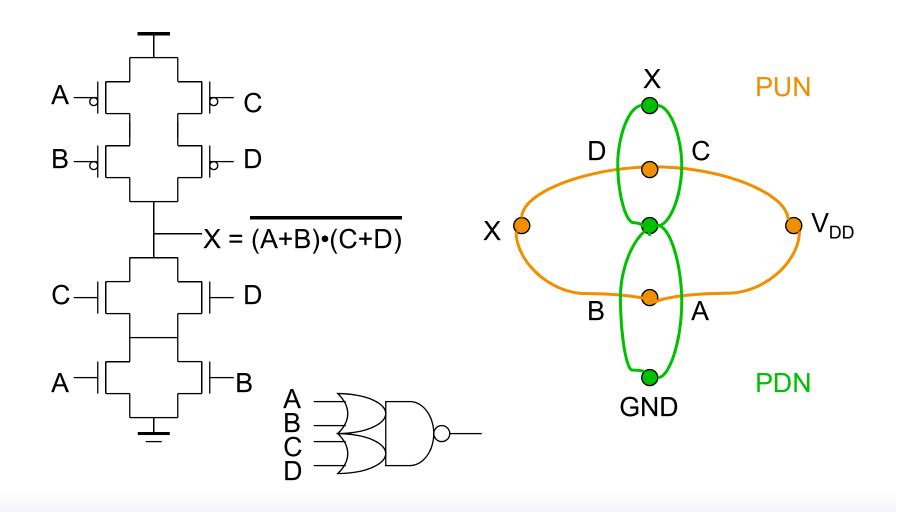

### OAI22 Logic Graph

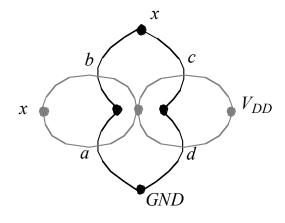

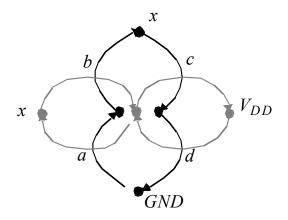

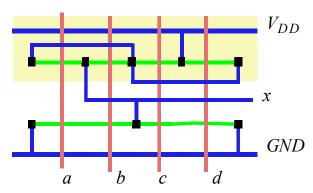

#### Example: x = ab+cd

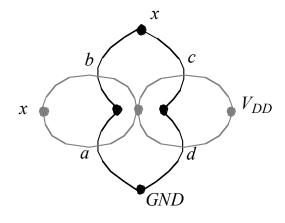

(a) Logic graphs for  $\overline{(ab+cd)}$

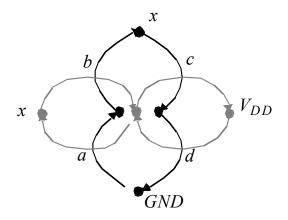

(b) Euler Paths  $\{a \ b \ c \ d\}$

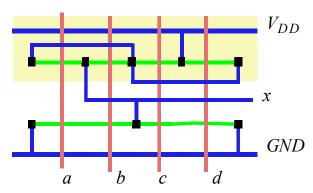

(c) stick diagram for ordering {a b c d}

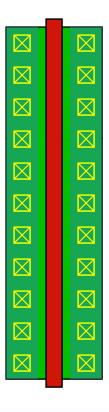

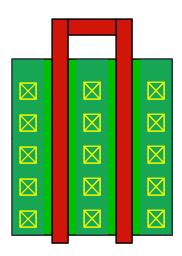

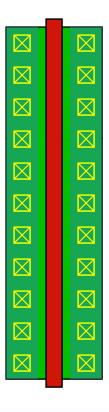

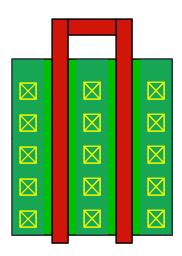

#### Multi-Fingered Transistors

One finger

Two fingers (folded)

Less diffusion capacitance

# Properties of Complementary CMOS Gates Snapshot

High noise margins:

$V_{OH}$  and  $V_{OL}$  are at  $V_{DD}$  and GND, respectively.

No static power consumption:

There never exists a direct path between  $V_{DD}$  and  $V_{SS}$  (GND) in steady-state mode.

Comparable rise and fall times:

(under appropriate sizing conditions)

#### Stick Diagrams

## Two Versions of C • (A + B)

#### Consistent Euler Path

### OAI22 Logic Graph

#### Example: x = ab+cd

(a) Logic graphs for  $\overline{(ab+cd)}$

(b) Euler Paths  $\{a \ b \ c \ d\}$

(c) stick diagram for ordering {a b c d}

#### Multi-Fingered Transistors

One finger

Two fingers (folded)

Less diffusion capacitance

# Properties of Complementary CMOS Gates Snapshot

High noise margins:

$V_{OH}$  and  $V_{OL}$  are at  $V_{DD}$  and GND, respectively.

No static power consumption:

There never exists a direct path between  $V_{DD}$  and  $V_{SS}$  (GND) in steady-state mode.

Comparable rise and fall times:

(under appropriate sizing conditions)