# **Cell Design**

Standard Cells

- General purpose logic

- Can be synthesized

- Same height, varying width

#### Datapath Cells

- For regular, structured designs (arithmetic)

- Includes some wiring in the cell

- Fixed height and width

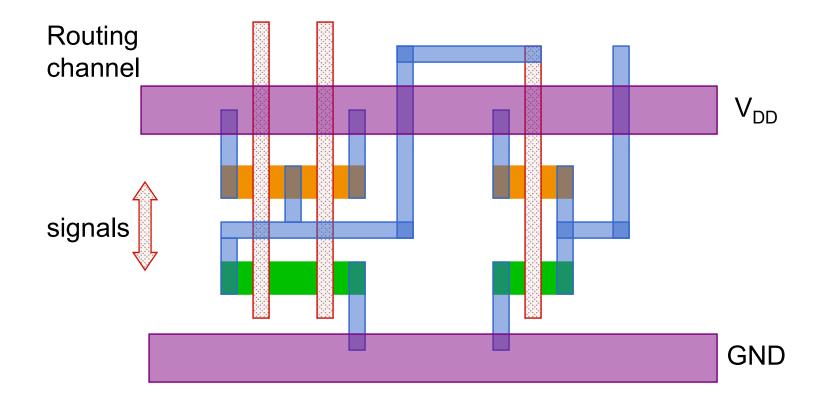

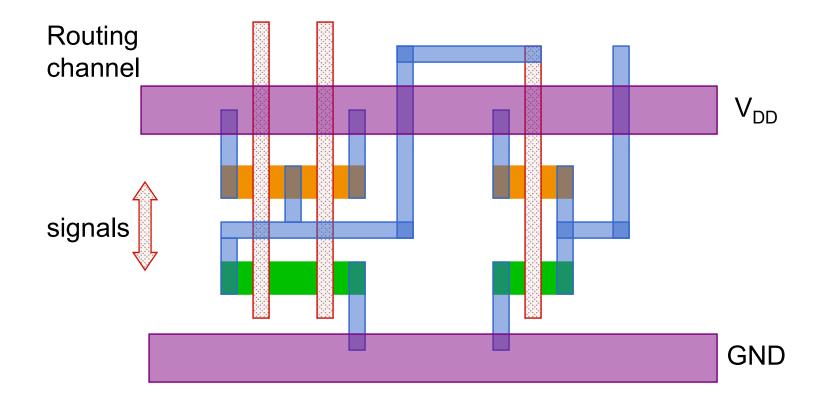

# Standard Cell Layout Methodology – 1980s

© Digital Integrated Circuits<sup>2nd</sup>

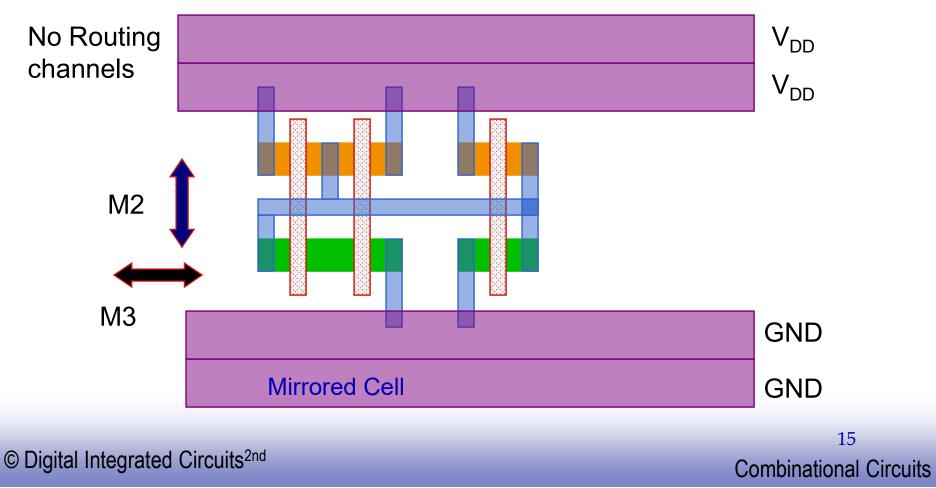

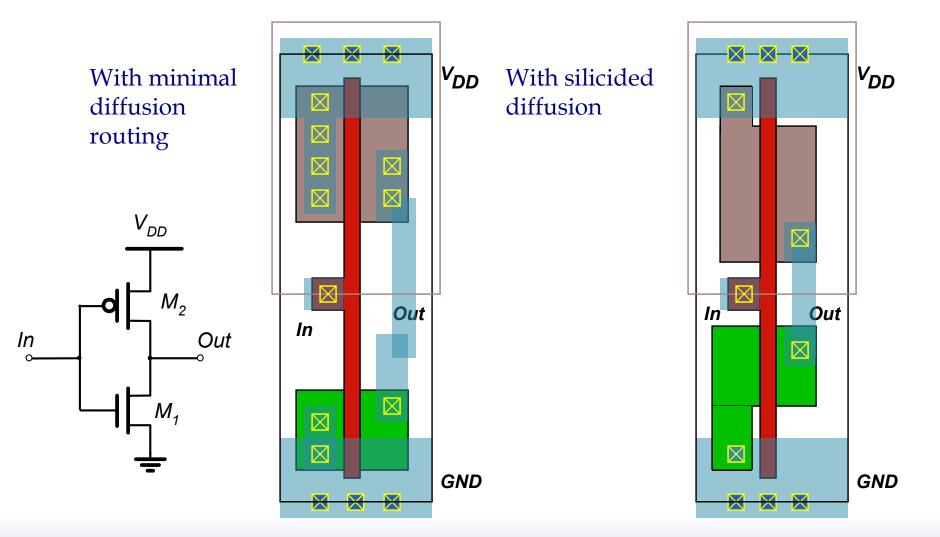

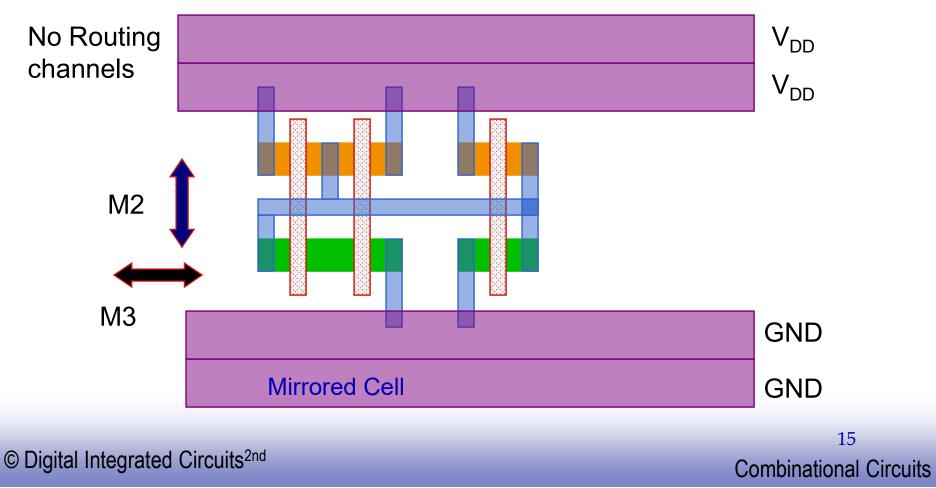

# Standard Cell Layout Methodology – 1990s

Mirrored Cell

© Digital Integrated Circuits<sup>2nd</sup>

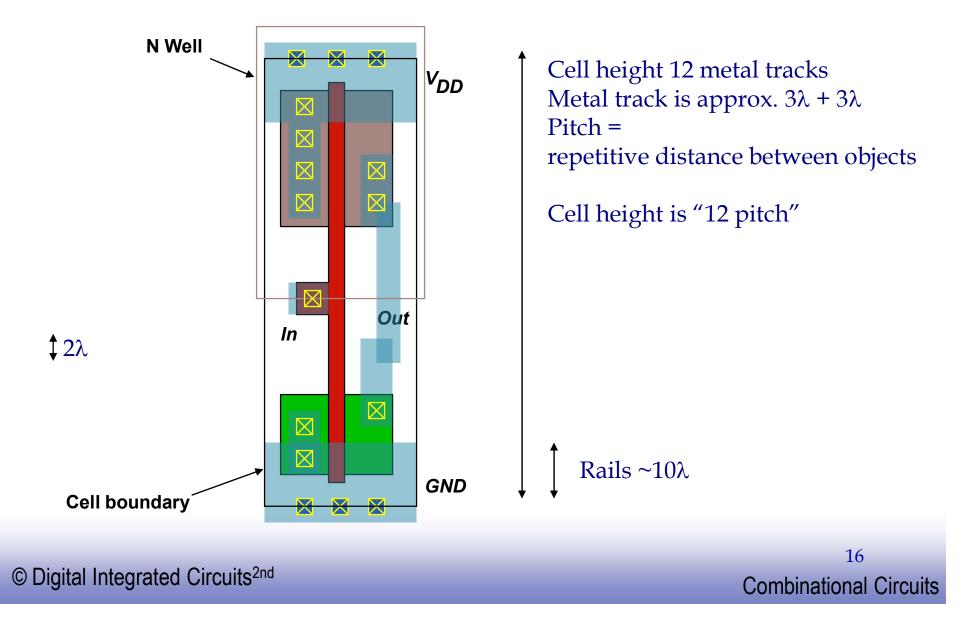

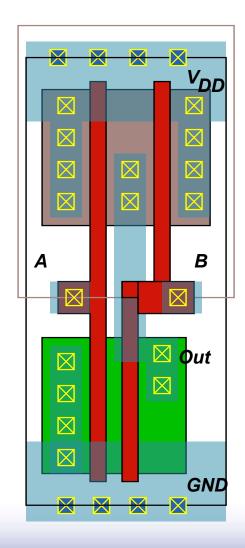

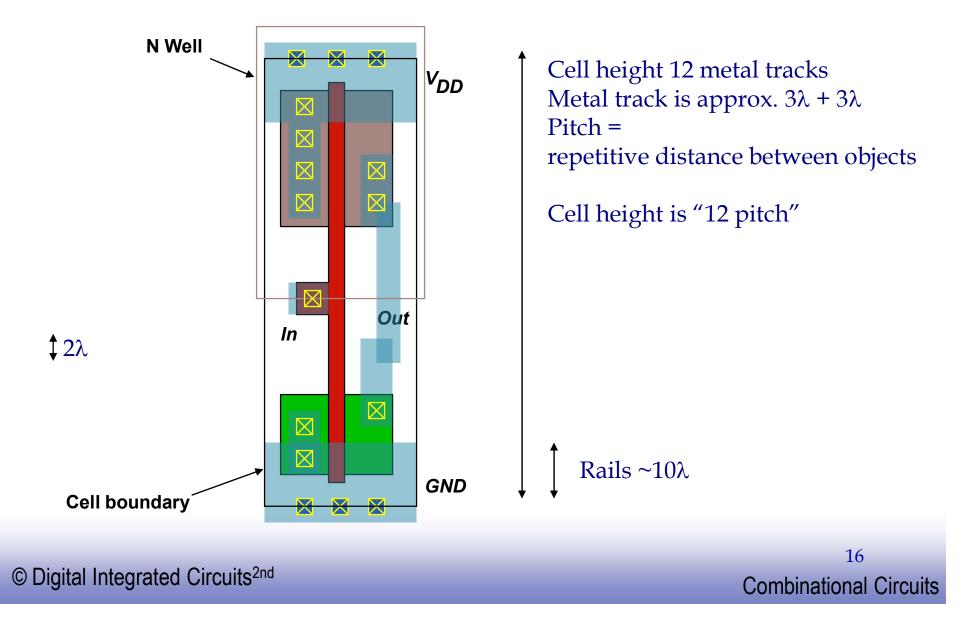

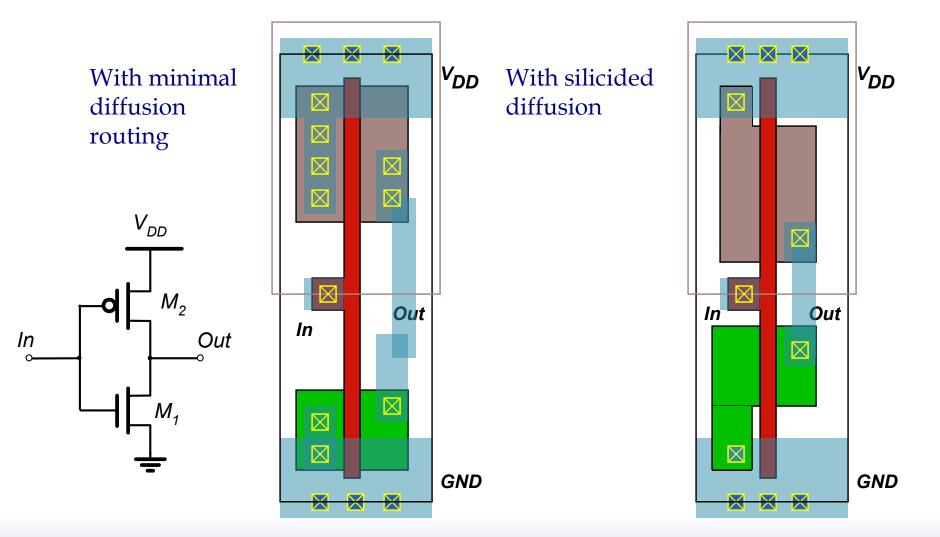

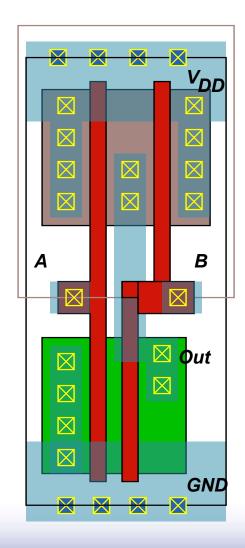

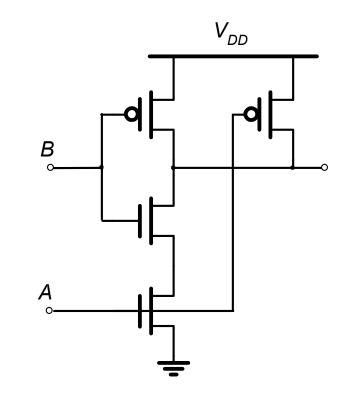

#### 2-input NAND gate

© Digital Integrated Circuits<sup>2nd</sup>

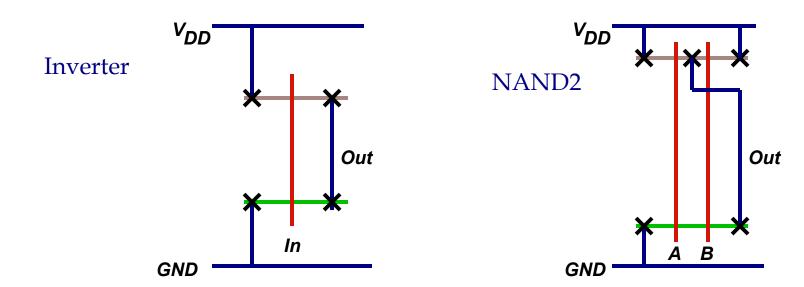

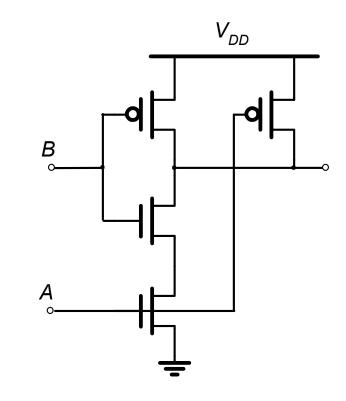

## **Stick Diagrams**

Contains no dimensions Represents relative positions of transistors

# **Cell Design**

Standard Cells

- General purpose logic

- Can be synthesized

- Same height, varying width

#### Datapath Cells

- For regular, structured designs (arithmetic)

- Includes some wiring in the cell

- Fixed height and width

# Standard Cell Layout Methodology – 1980s

© Digital Integrated Circuits<sup>2nd</sup>

# Standard Cell Layout Methodology – 1990s

Mirrored Cell

© Digital Integrated Circuits<sup>2nd</sup>

#### 2-input NAND gate

© Digital Integrated Circuits<sup>2nd</sup>

## **Stick Diagrams**

Contains no dimensions Represents relative positions of transistors