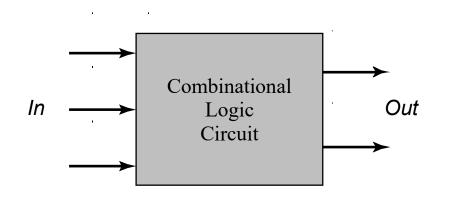

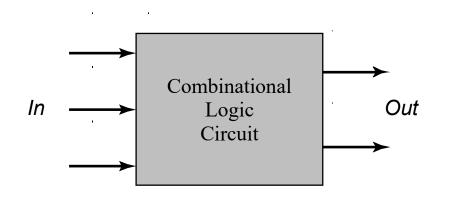

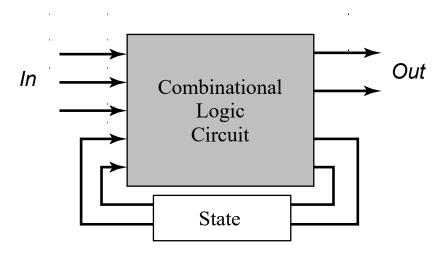

#### Combinational vs. Sequential Logic

Combinational

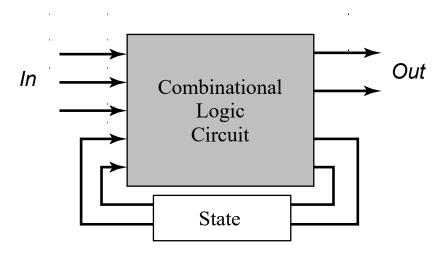

Sequential

Output =

$$f(In)$$

Output = f(In, Previous In)

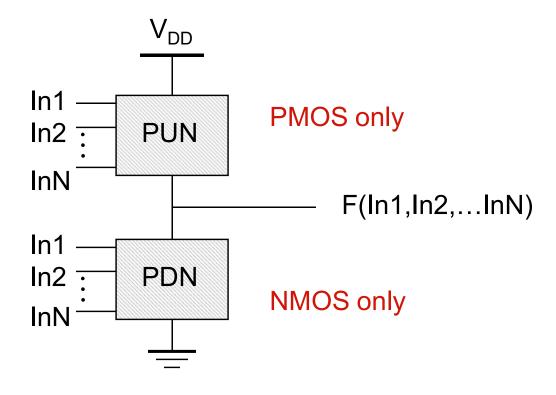

#### Static CMOS Circuit

At every point in time (except during the switching transients) each gate output is connected to either  $V_{DD}$  or  $V_{ss}$  via a low-resistive path.

The outputs of the gates assume at all times the value of the Boolean function, implemented by the circuit (ignoring, once again, the transient effects during switching periods).

This is in contrast to the *dynamic* circuit class, which relies on temporary storage of signal values on the capacitance of high impedance circuit nodes.

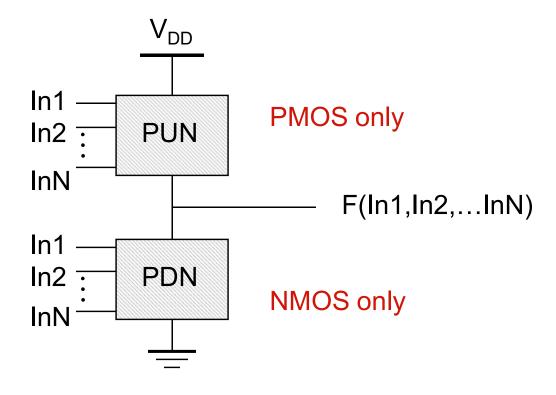

## Static Complementary CMOS

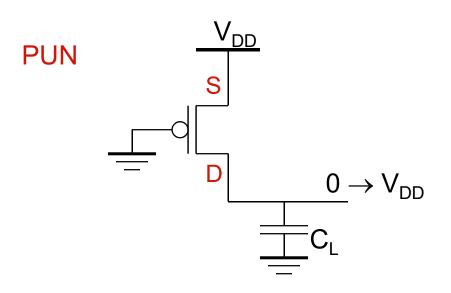

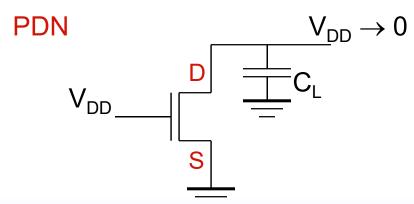

PUN and PDN are dual logic networks

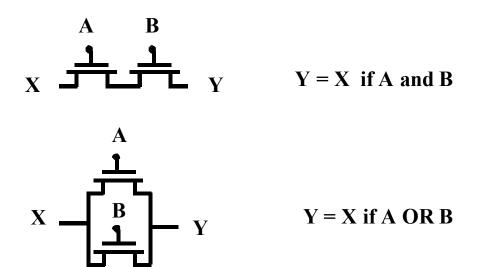

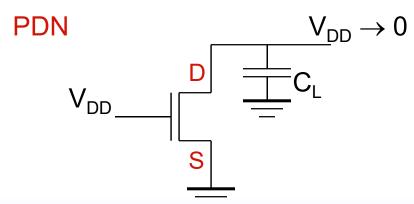

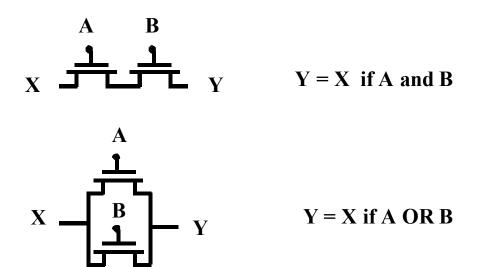

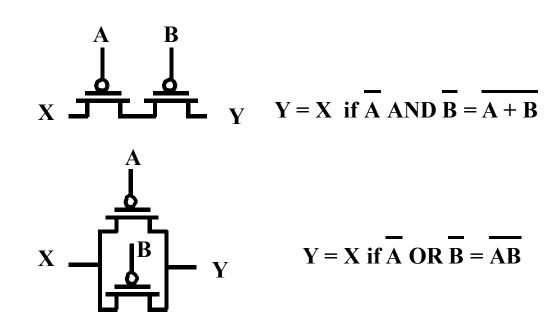

# NMOS Transistors in Series/Parallel Connection

Transistors can be thought as a switch controlled by its gate signal

NMOS switch closes when switch control input is high

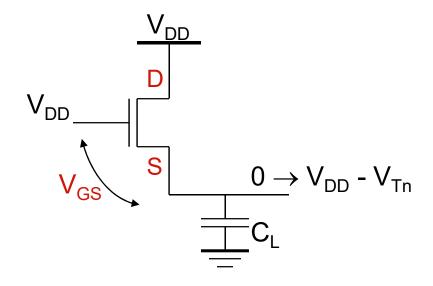

NMOS Transistors pass a "strong" 0 but a "weak" 1

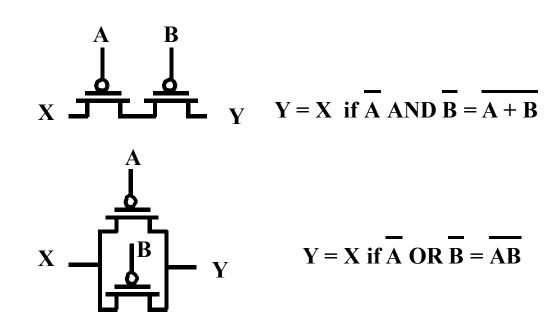

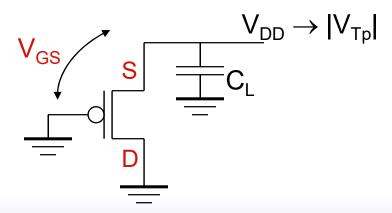

# PMOS Transistors in Series/Parallel Connection

PMOS switch closes when switch control input is low

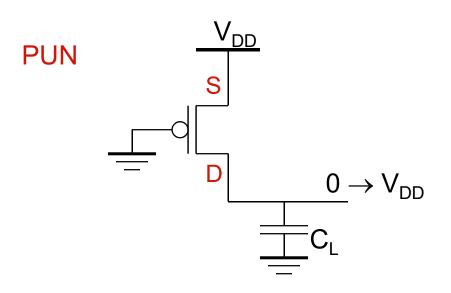

PMOS Transistors pass a "strong" 1 but a "weak" 0

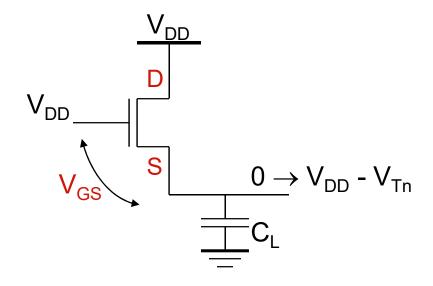

### Threshold Drops

7

# Complementary CMOS Logic Style

• PUP is the <u>DUAL</u> of PDN (can be shown using DeMorgan's Theorem's)

$$\overline{A+B} = \overline{A}\overline{B}$$

$$\overline{AB} = \overline{A} + \overline{B}$$

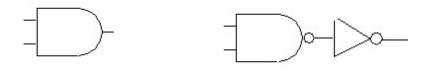

The complementary gate is inverting

$$AND = NAND + INV$$

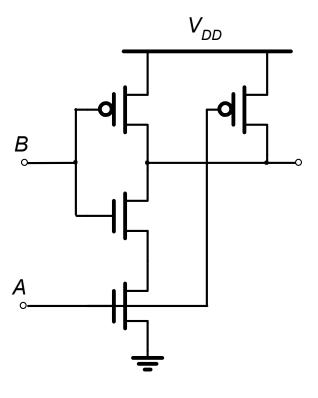

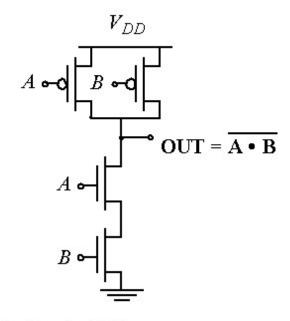

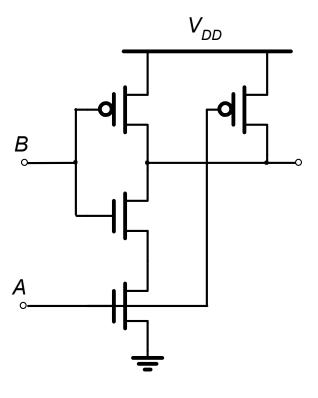

### Example Gate: NAND

| $\mathbf{A}$ | В | Out |

|--------------|---|-----|

| 0            | 0 | 1   |

| 0            | 1 | 1   |

| 1            | 0 | 1   |

| 1            | 1 | 0   |

gate

PDN:

$$G = A B \Rightarrow Conduction to GND$$

PUN:

$$F = \overline{A} + \overline{B} = \overline{AB} \Rightarrow Conduction to V_{DD}$$

$$G(In_1,In_2,In_3,\ldots) \equiv F(\overline{In_1},\overline{In_2},\overline{In_3},\ldots)$$

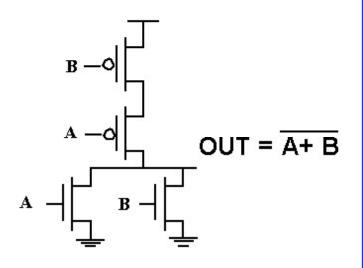

## Example Gate: NOR

| A | В | Out |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 0   |

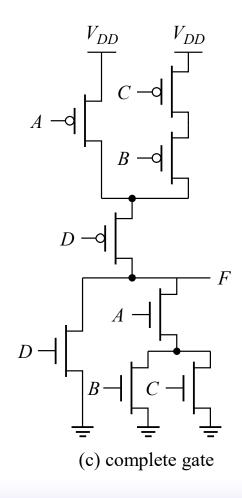

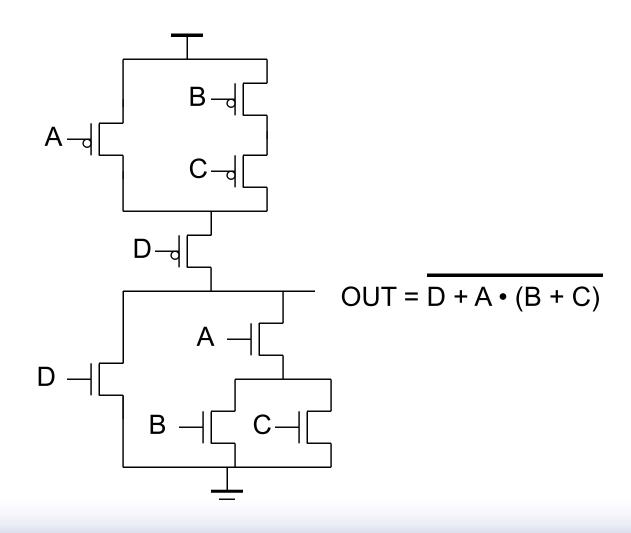

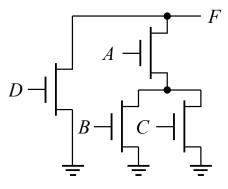

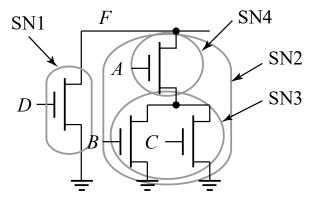

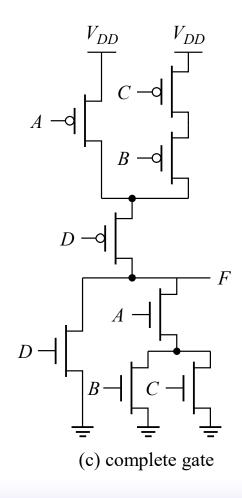

# **Complex CMOS Gate**

### Constructing a Complex Gate

(a) pull-down network

(b) Deriving the pull-up network hierarchically by identifying sub-nets

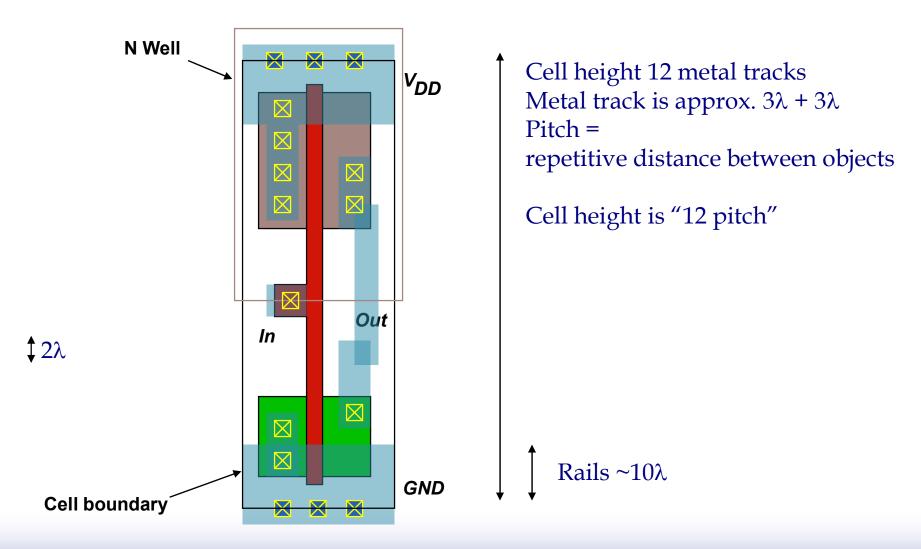

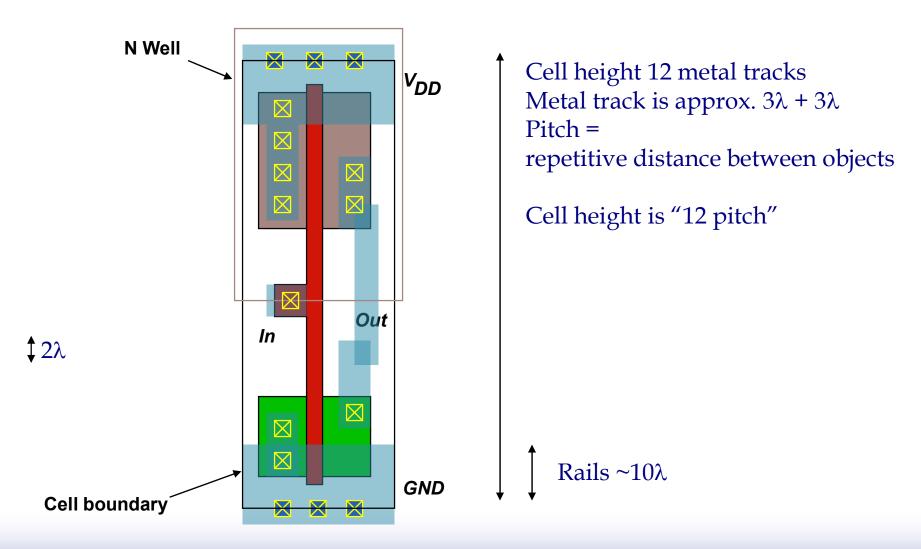

# Cell Design

#### □ Standard Cells

- General purpose logic

- Can be synthesized

- Same height, varying width

#### □ Datapath Cells

- For regular, structured designs (arithmetic)

- Includes some wiring in the cell

- Fixed height and width

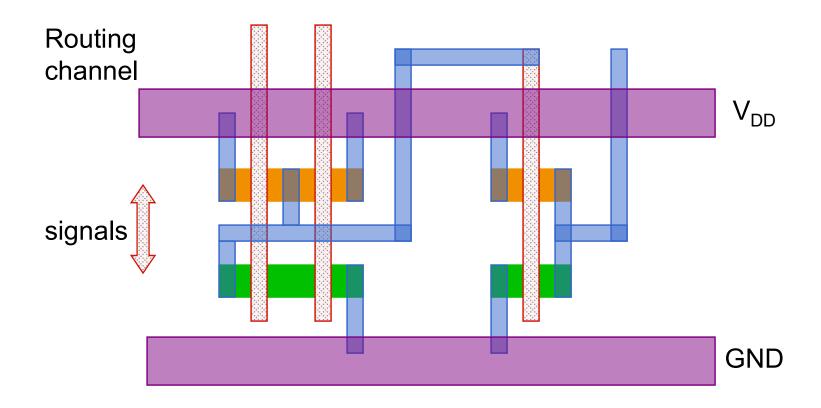

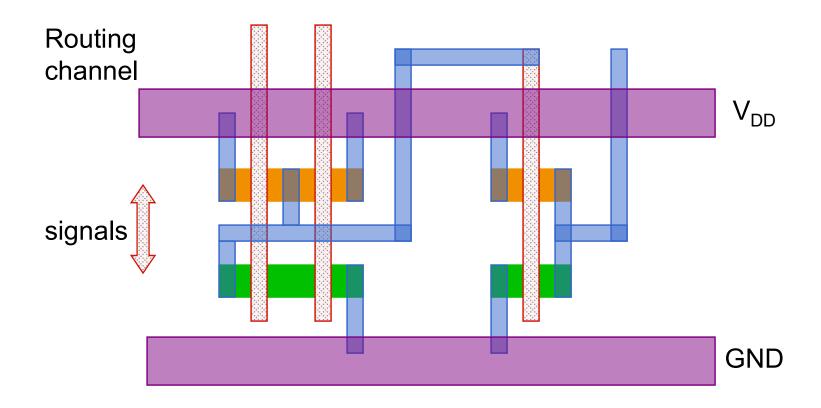

# Standard Cell Layout Methodology – 1980s

# Standard Cell Layout Methodology – 1990s

### Mirrored Cell No Routing channels M2 M3 **GND** Mirrored Cell **GND**

With minimal diffusion routing

With silicided diffusion

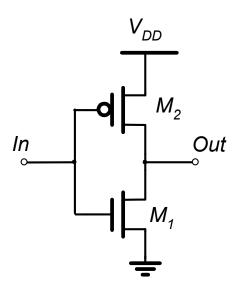

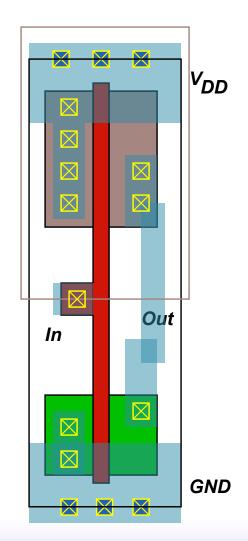

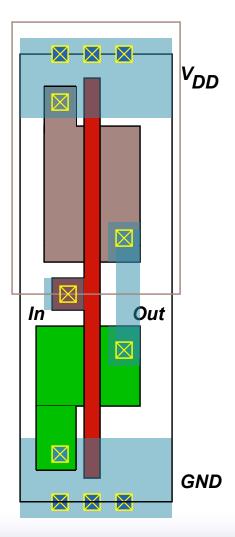

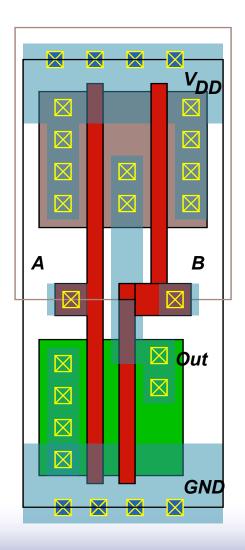

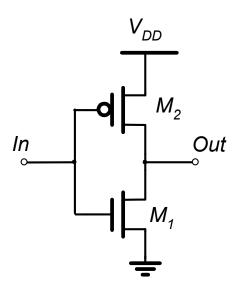

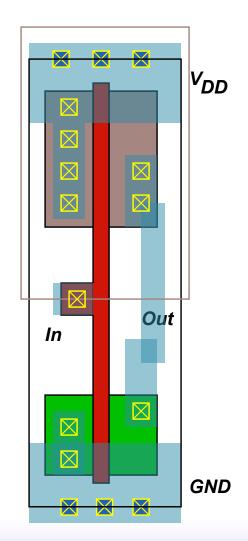

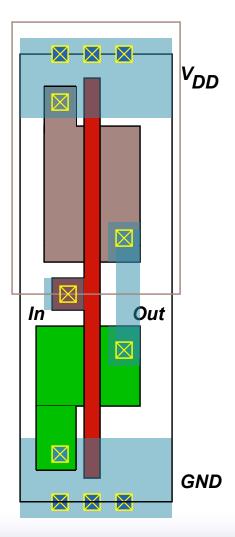

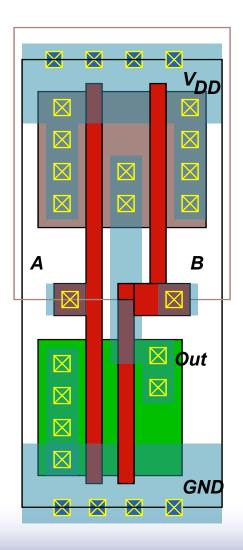

#### 2-input NAND gate

#### Combinational vs. Sequential Logic

Combinational

Sequential

Output =

$$f(In)$$

Output = f(In, Previous In)

#### Static CMOS Circuit

At every point in time (except during the switching transients) each gate output is connected to either  $V_{DD}$  or  $V_{ss}$  via a low-resistive path.

The outputs of the gates assume at all times the value of the Boolean function, implemented by the circuit (ignoring, once again, the transient effects during switching periods).

This is in contrast to the *dynamic* circuit class, which relies on temporary storage of signal values on the capacitance of high impedance circuit nodes.

## Static Complementary CMOS

PUN and PDN are dual logic networks

# NMOS Transistors in Series/Parallel Connection

Transistors can be thought as a switch controlled by its gate signal

NMOS switch closes when switch control input is high

NMOS Transistors pass a "strong" 0 but a "weak" 1

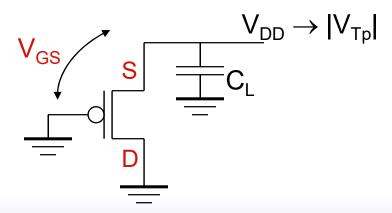

# PMOS Transistors in Series/Parallel Connection

PMOS switch closes when switch control input is low

PMOS Transistors pass a "strong" 1 but a "weak" 0

### Threshold Drops

7

# Complementary CMOS Logic Style

• PUP is the <u>DUAL</u> of PDN (can be shown using DeMorgan's Theorem's)

$$\overline{A+B} = \overline{A}\overline{B}$$

$$\overline{AB} = \overline{A} + \overline{B}$$

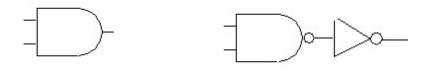

The complementary gate is inverting

$$AND = NAND + INV$$

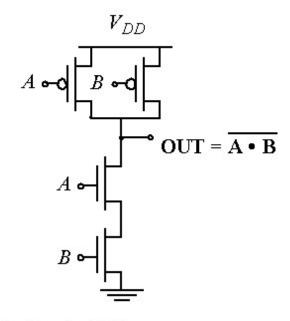

### Example Gate: NAND

| $\mathbf{A}$ | В | Out |

|--------------|---|-----|

| 0            | 0 | 1   |

| 0            | 1 | 1   |

| 1            | 0 | 1   |

| 1            | 1 | 0   |

gate

PDN:

$$G = A B \Rightarrow Conduction to GND$$

PUN:

$$F = \overline{A} + \overline{B} = \overline{AB} \Rightarrow Conduction to V_{DD}$$

$$G(In_1,In_2,In_3,\ldots) \equiv F(\overline{In_1},\overline{In_2},\overline{In_3},\ldots)$$

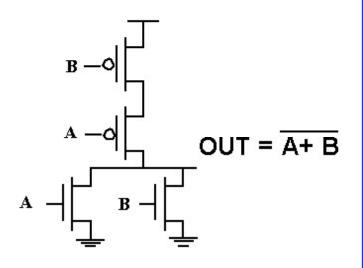

## Example Gate: NOR

| A | В | Out |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 0   |

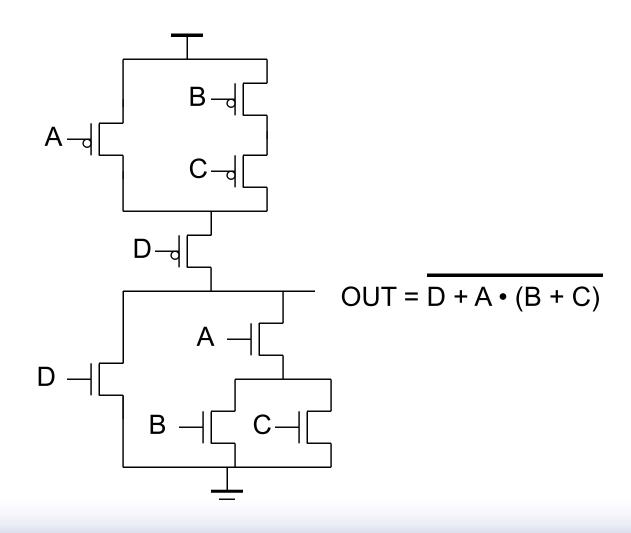

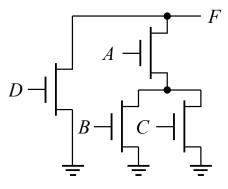

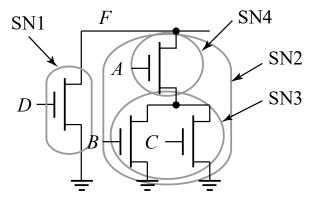

# **Complex CMOS Gate**

### Constructing a Complex Gate

(a) pull-down network

(b) Deriving the pull-up network hierarchically by identifying sub-nets

# Cell Design

#### □ Standard Cells

- General purpose logic

- Can be synthesized

- Same height, varying width

#### □ Datapath Cells

- For regular, structured designs (arithmetic)

- Includes some wiring in the cell

- Fixed height and width

# Standard Cell Layout Methodology – 1980s

# Standard Cell Layout Methodology – 1990s

### Mirrored Cell No Routing channels M2 M3 **GND** Mirrored Cell **GND**

With minimal diffusion routing

With silicided diffusion

#### 2-input NAND gate