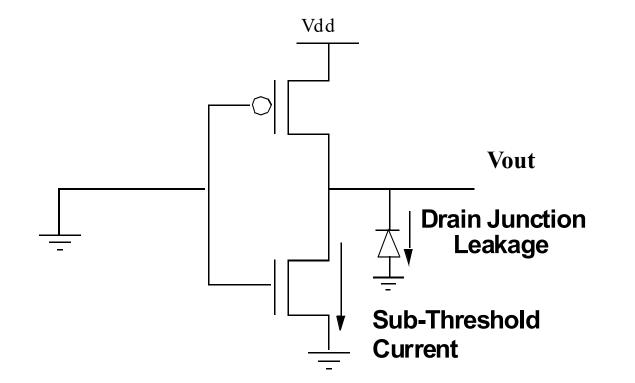

### Leakage

Sub-threshold current one of most compelling issues in low-energy circuit design!

© Digital Integrated Circuits<sup>2nd</sup>

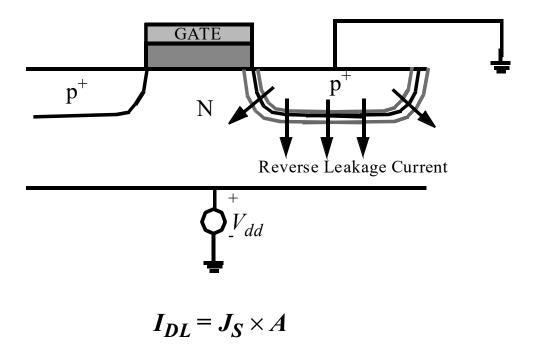

#### **Reverse-Biased Diode Leakage**

$JS = 10-100 \text{ pA}/\mu\text{m2}$  at 25 deg C for  $0.25\mu\text{m}$  CMOS JS doubles for every 9 deg C!

© Digital Integrated Circuits<sup>2nd</sup>

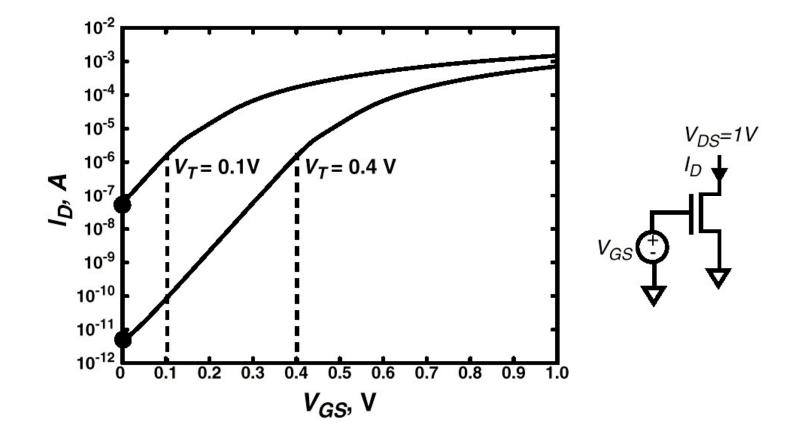

#### Subthreshold Leakage Component

Leakage control is critical for low-voltage operation

© Digital Integrated Circuits<sup>2nd</sup>

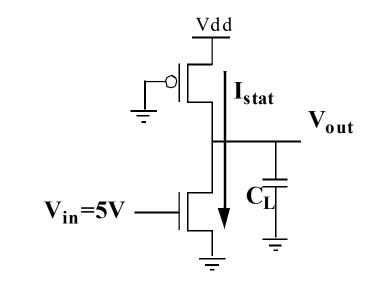

## **Static Power Consumption**

$P_{stat} = P_{(In=1)} V_{dd} I_{stat}$

Wasted energy ... Should be avoided in almost all cases, but could help reducing energy in others (e.g. sense amps)

© Digital Integrated Circuits<sup>2nd</sup>

#### **Principles for Power Reduction**

□ Prime choice: Reduce voltage!

- Recent years have seen an acceleration in supply voltage reduction

- Design at very low voltages still open question (0.6 ... 0.9 V by 2010!)

- Reduce switching activity

- Reduce physical capacitance

- Device Sizing: for F=20

$-f_{opt}(energy)=3.53, f_{opt}(performance)=4.47$

# Impact of Technology Scaling

© Digital Integrated Circuits<sup>2nd</sup>

# **Goals of Technology Scaling**

□ Make things cheaper:

- Want to sell more functions (transistors) per chip for the same money

- Build same products cheaper, sell the same part for less money

- Price of a transistor has to be reduced

- But also want to be faster, smaller, lower power

# **Technology Scaling**

□ Goals of scaling the dimensions by 30%:

- Reduce gate delay by 30% (increase operating frequency by 43%)

- Double transistor density

- Reduce energy per transition by 65% (50% power savings @ 43% increase in frequency

- Die size used to increase by 14% per generation

- □ Technology generation spans 2-3 years

### **Technology Generations**

| 95        | 96  | 97        | 98 | 99         | 00 | 01        | 02 | 03        | 04 | 05 | 06    | 07 | 06     | 09 |

|-----------|-----|-----------|----|------------|----|-----------|----|-----------|----|----|-------|----|--------|----|

| 350<br>nm | 1   | 2         | з  | 4          | 5  | 100       |    | 12.6      |    |    | Oat . |    | 1.00   |    |

| -2        | -1  | 250<br>nm | 1  | 2          | 3  | 4         | 5  |           |    |    |       |    |        |    |

| -4        | -3  | ş         | -1 | 180<br>rim | 1  | 2         | а  | 4         | 5  |    | NONE  |    | 1      |    |

| -8        | 5   | Ą         | -3 | -2         | -1 | 150<br>nm | 1  | 2         | в  | 4  | 6     |    | E CONT |    |

| -8        | -7  | -6        | -5 | Ŧ          | -3 | -2        | -1 | 130<br>nm | 1  | 2  | 8     | 4  | 6      |    |

| -11       | -10 | -9        | -8 | -7         | -6 | -5        | -4 | -3        | -2 | -1 | 100   | 1  | 2      | з  |

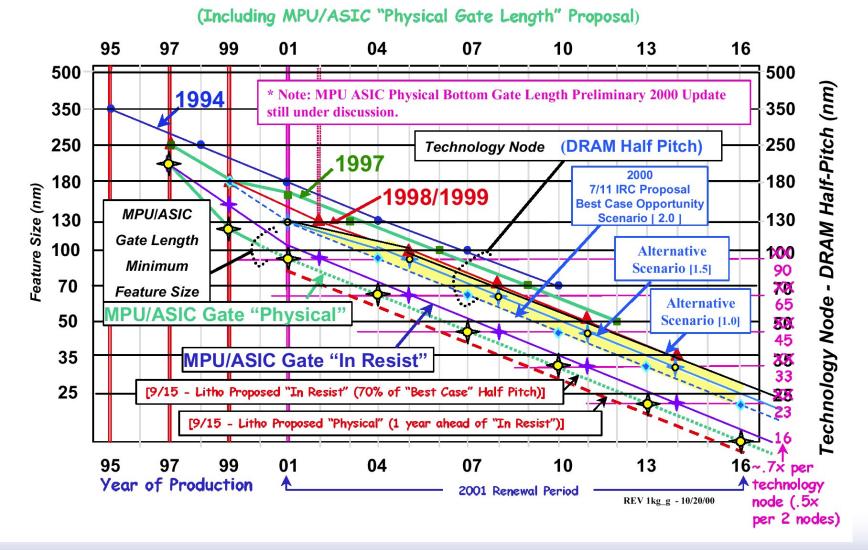

#### **Technology Evolution (2000 data)**

#### International Technology Roadmap for Semiconductors

| Year of<br>Introduction             | 1999    | 2000    | 2001    | 2004    | 2008    | 2011    | 2014         |

|-------------------------------------|---------|---------|---------|---------|---------|---------|--------------|

| Technology node<br>[nm]             | 180     |         | 130     | 90      | 60      | 40      | 30           |

| Supply [V]                          | 1.5-1.8 | 1.5-1.8 | 1.2-1.5 | 0.9-1.2 | 0.6-0.9 | 0.5-0.6 | 0.3-0.6      |

| Wiring levels                       | 6-7     | 6-7     | 7       | 8       | 9       | 9-10    | 10           |

| Max frequency<br>[GHz],Local-Global | 1.2     | 1.6-1.4 | 2.1-1.6 | 3.5-2   | 7.1-2.5 | 11-3    | 14.9<br>-3.6 |

| Max μP power [W]                    | 90      | 106     | 130     | 160     | 171     | 177     | 186          |

| Bat. power [W]                      | 1.4     | 1.7     | 2.0     | 2.4     | 2.1     | 2.3     | 2.5          |

Node years: 2007/65nm, 2010/45nm, 2013/33nm, 2016/23nm

© Digital Integrated Circuits<sup>2nd</sup>

#### **Technology Evolution (1999)**

| Year of Introduction                              | 1994 | <b>199</b> 7 | 2000 | 2003 | 2006 | 2009 |

|---------------------------------------------------|------|--------------|------|------|------|------|

| Channel length (µm)                               | 0.4  | 0.3          | 0.25 | 0.18 | 0.13 | 0.1  |

| Gate oxide (nm)                                   | 12   | 7            | 6    | 4.5  | 4    | 4    |

| $V_{DD}$ (V)                                      | 3.3  | 2.2          | 2.2  | 1.5  | 1.5  | 1.5  |

| $V_T(\mathbf{V})$                                 | 0.7  | 0.7          | 0.7  | 0.6  | 0.6  | 0.6  |

| NMOS $I_{Dsat}$ (mA/µm)<br>(@ $V_{GS} = V_{DD}$ ) | 0.35 | 0.27         | 0.31 | 0.21 | 0.29 | 0.33 |

| PMOS $I_{Dsat}$ (mA/µm)<br>(@ $V_{GS} = V_{DD}$ ) | 0.16 | 0.11         | 0.14 | 0.09 | 0.13 | 0.16 |

•

#### ITRS Technology Roadmap Acceleration Continues

© Digital Integrated Circuits<sup>2nd</sup>

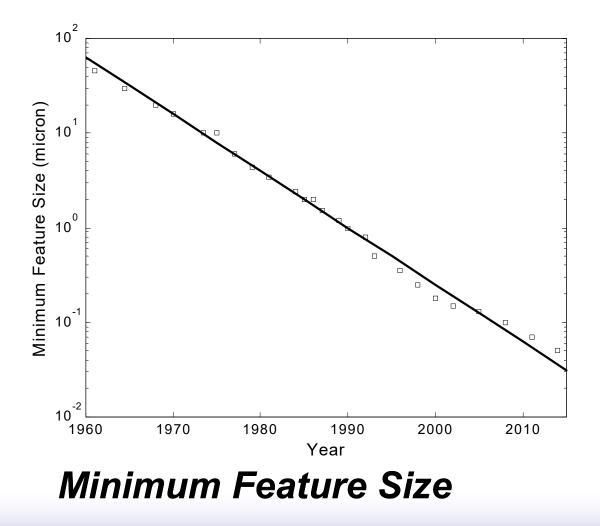

## **Technology Scaling (1)**

© Digital Integrated Circuits<sup>2nd</sup>

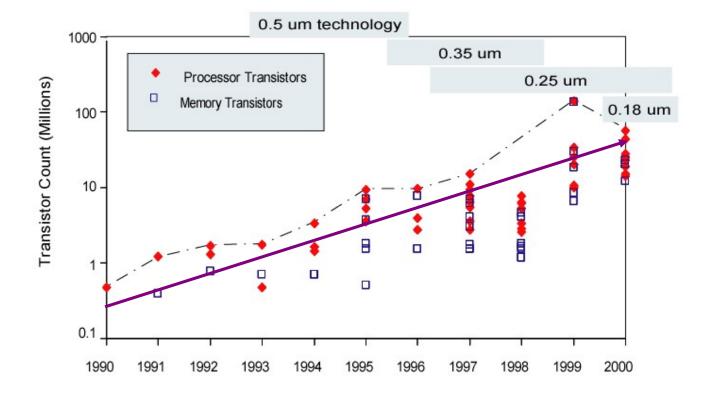

# **Technology Scaling (2)**

Number of components per chip

## **Technology Scaling (3)**

© Digital Integrated Circuits<sup>2nd</sup>

#### **Technology Scaling (4)**

From Kuroda

© Digital Integrated Circuits<sup>2nd</sup>

## **Technology Scaling Models**

#### • Full Scaling (Constant Electrical Field)

ideal model — dimensions and voltage scale together by the same factor S

#### Fixed Voltage Scaling

most common model until recently — only dimensions scale, voltages remain constant

#### General Scaling

most realistic for todays situation — voltages and dimensions scale with different factors

#### **Scaling Relationships for Long Channel Devices**

| Parameter                        | Relation                           | Full<br>Scaling  | General<br>Scaling | Fixed Voltage<br>Scaling |

|----------------------------------|------------------------------------|------------------|--------------------|--------------------------|

| W, L, t <sub>ox</sub>            |                                    | 1/S              | 1/S                | 1/S                      |

| V <sub>DD</sub> , V <sub>T</sub> |                                    | 1/S              | 1/U                | 1                        |

| N <sub>SUB</sub>                 | V/W <sub>depl</sub> <sup>2</sup>   | S                | S <sup>2</sup> /U  | S <sup>2</sup>           |

| Area/Device                      | WL                                 | 1/S <sup>2</sup> | 1/S <sup>2</sup>   | 1/S <sup>2</sup>         |

| Cox                              | 1/t <sub>ox</sub>                  | S                | S                  | S                        |

| CL                               | C <sub>ox</sub> WL                 | 1/S              | 1/S                | 1/S                      |

| k <sub>n</sub> , k <sub>p</sub>  | C <sub>ox</sub> W/L                | S                | S                  | S                        |

| I <sub>av</sub>                  | $k_{n,p} V^2$                      | 1/S              | S/U <sup>2</sup>   | S                        |

| t <sub>p</sub> (intrinsic)       | C <sub>L</sub> V / I <sub>av</sub> | 1/S              | U/S <sup>2</sup>   | 1/S <sup>2</sup>         |

| Pav                              | $\frac{C_L V^2 / t_p}{C_L V^2}$    | 1/S <sup>2</sup> | S/U <sup>3</sup>   | S                        |

| PDP                              | $C_L V^2$                          | 1/S <sup>3</sup> | $1/\mathrm{SU}^2$  | 1/S                      |

## Transistor Scaling (velocity-saturated devices)

| Parameter                                    | Relation               | Full Scaling | General Scaling | Fixed-Voltage Scaling |  |

|----------------------------------------------|------------------------|--------------|-----------------|-----------------------|--|

| <i>W</i> , <i>L</i> , <i>t</i> <sub>ox</sub> |                        | 1/S          | 1/S             | 1/S                   |  |

| $V_{DD}$ $V_T$                               |                        | 1/S          | 1/U             | 1                     |  |

| $N_{SUB}$                                    | $V/W_{depl}^2$         | S            | $S^2/U$         | $S^2$                 |  |

| Area/Device                                  | WL                     | $1/S^2$      | $1/S^2$         | $1/S^2$               |  |

| C <sub>ox</sub>                              | $1/t_{ox}$             | S            | S               | S                     |  |

| $C_{gate}$                                   | $C_{ox}WL$             | 1/S          | 1/S             | 1/S                   |  |

| $k_{n}$ $k_{p}$                              | C <sub>ox</sub> W/L    | S            | S               | S                     |  |

| I <sub>sat</sub>                             | $C_{ox}WV$             | 1/S          | 1/U             | 1                     |  |

| Current Density                              | I <sub>sat</sub> /Area | S            | $S^2/U$         | $S^2$                 |  |

| Ron                                          | V/I <sub>sat</sub>     | 1            | 1               | 1                     |  |

| Intrinsic Delay                              | $R_{on}C_{gate}$       | 1/S          | 1/S             | 1/S                   |  |

| Р                                            | $I_{sat}V$             | $1/S^2$      | $1/U^2$         | 1                     |  |

| Power Density                                | P/Area                 | 1            | $S^2/U^2$       | $S^2$                 |  |

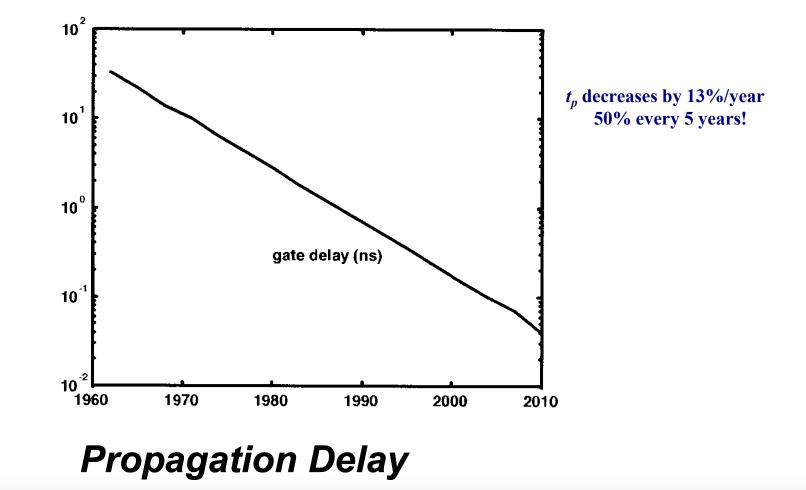

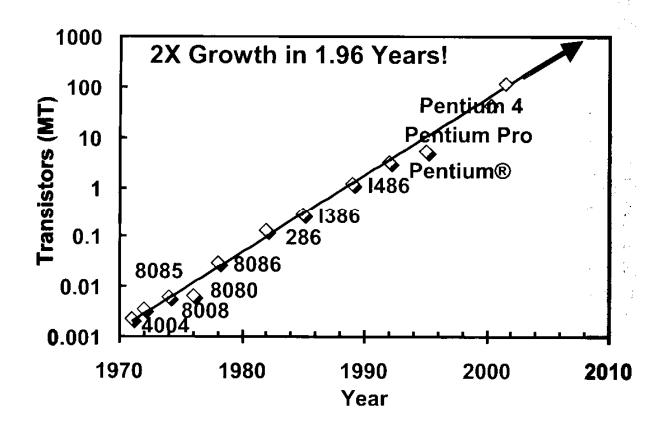

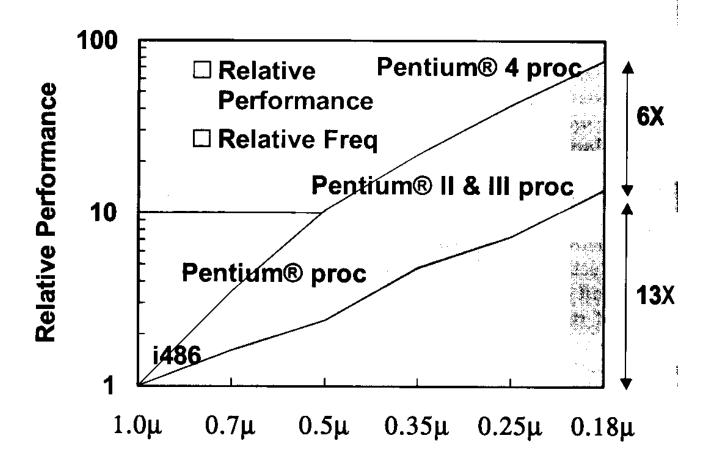

#### μ**Processor Scaling**

P.Gelsinger: µProcessors for the New Millenium, ISSCC 2001

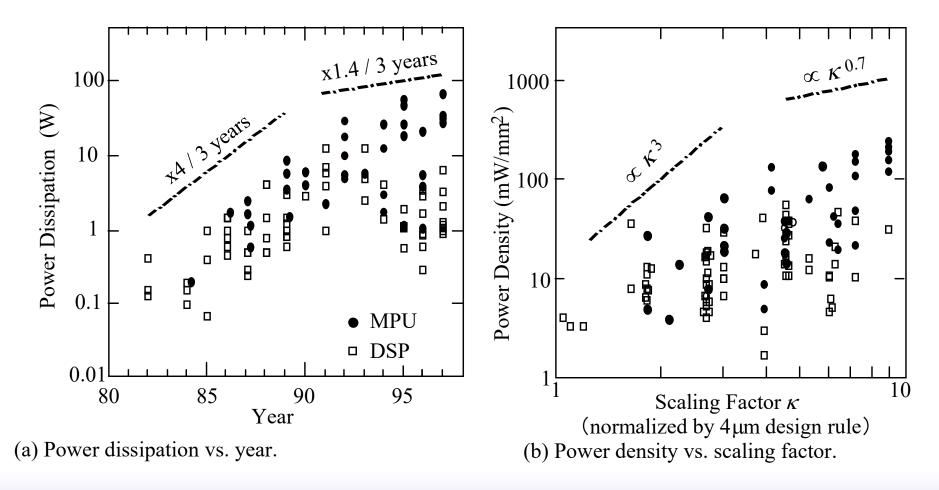

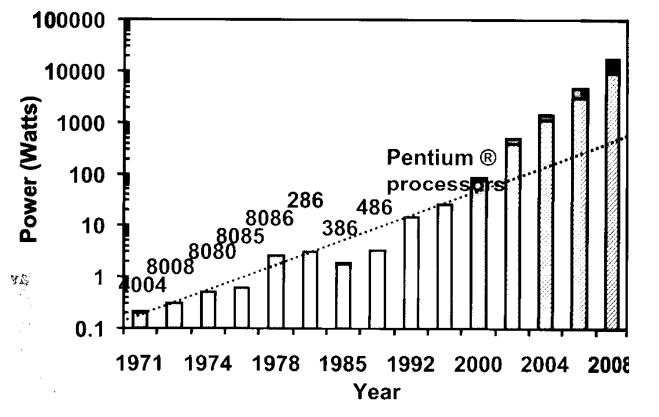

#### μ**Processor Power**

P.Gelsinger:  $\mu$ Processors for the New Millenium, ISSCC 2001

#### μ**Processor Performance**

P.Gelsinger: µProcessors for the New Millenium, ISSCC 2001

#### 2010 Outlook

#### □ Performance 2X/16 months

- 1 TIP (terra instructions/s)

- 30 GHz clock

- □ Size

- No of transistors: 2 Billion

- Die: 40\*40 mm

- Power

- 10kW!!

- Leakage: 1/3 active Power

P.Gelsinger:  $\mu$ Processors for the New Millenium, ISSCC 2001

# Some interesting questions

What will cause this model to break?

When will it break?

□ Will the model gradually slow down?

- Power and power density

- Leakage

- Process Variation