# **Propagation Delay**

© Digital Integrated Circuits<sup>2nd</sup>

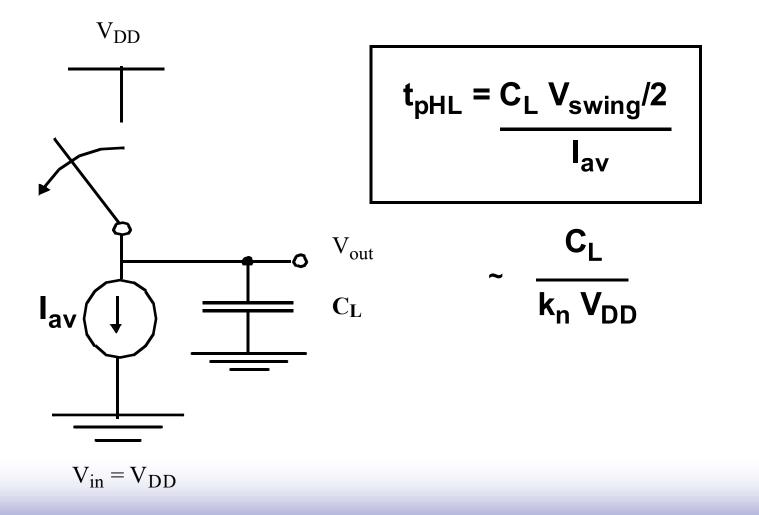

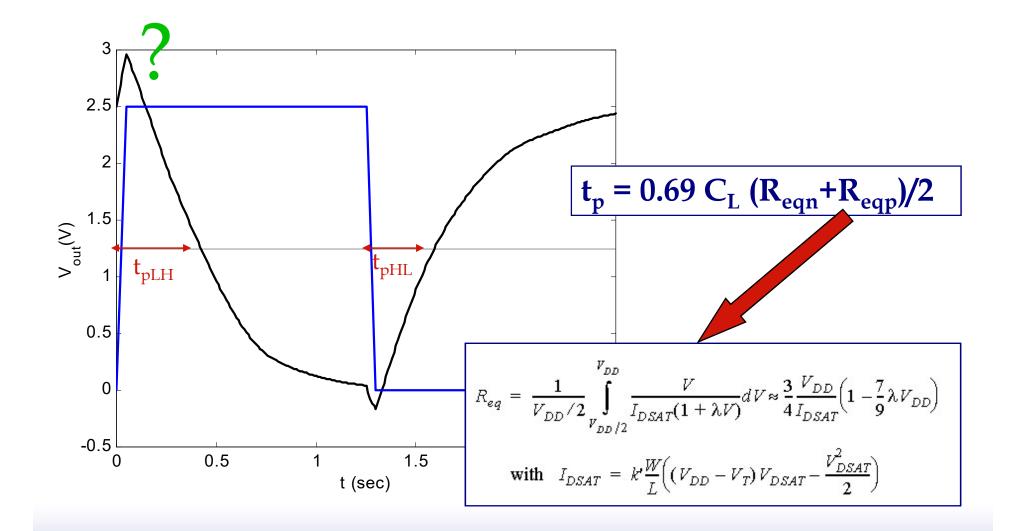

## **CMOS Inverter Propagation Delay Approach 1**

© Digital Integrated Circuits<sup>2nd</sup>

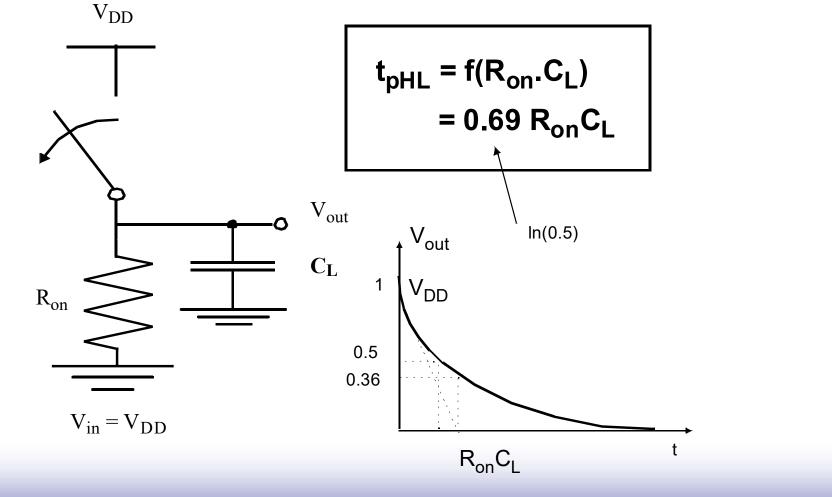

## **CMOS Inverter Propagation Delay Approach 2**

© Digital Integrated Circuits<sup>2nd</sup>

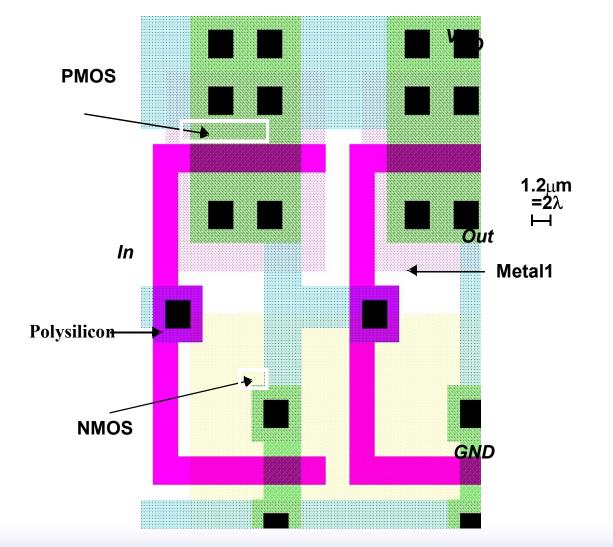

#### **CMOS Inverters**

© Digital Integrated Circuits<sup>2nd</sup>

#### **Transient Response**

© Digital Integrated Circuits<sup>2nd</sup>

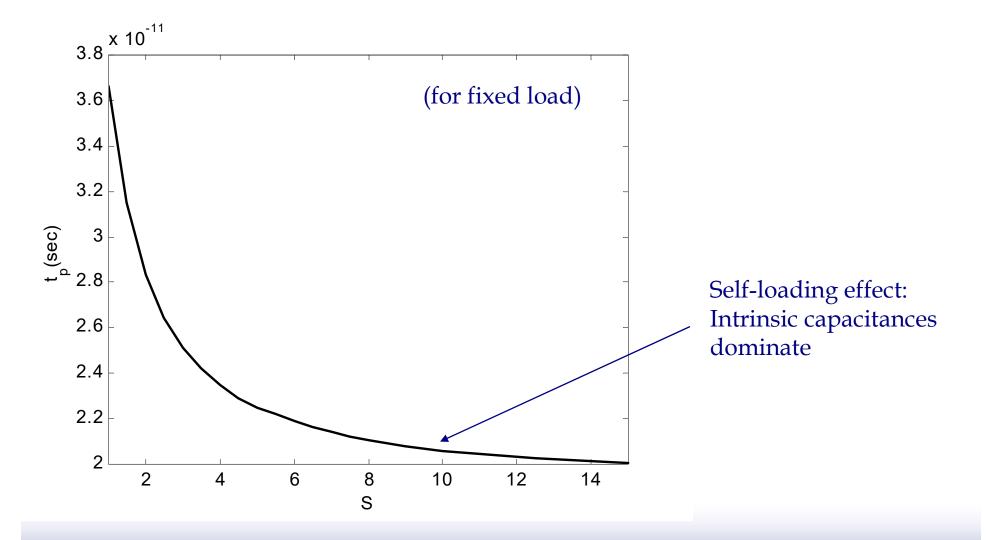

## **Design for Performance**

Keep capacitances small

Increase transistor sizes

watch out for self-loading!

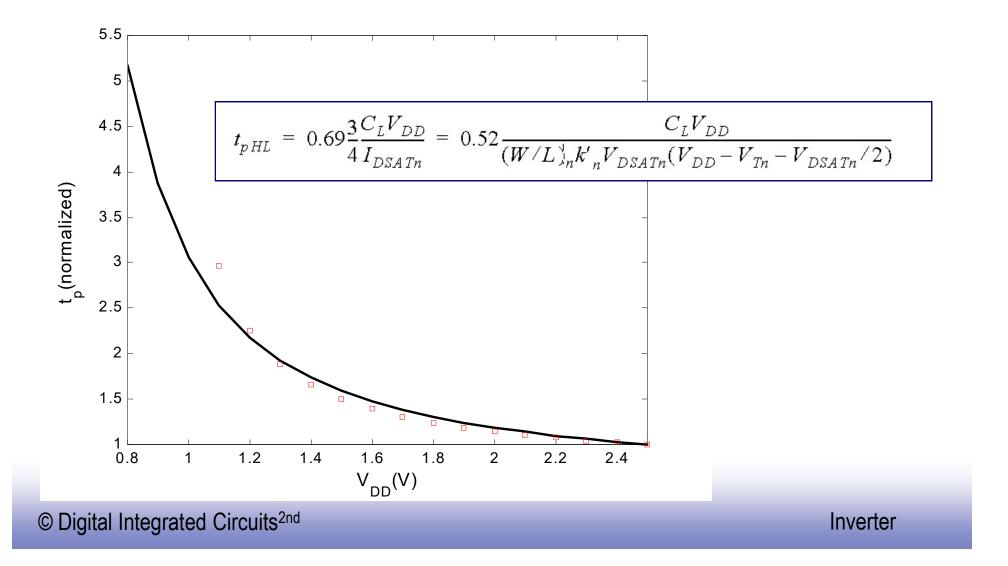

Increase V<sub>DD</sub> (???)

# **Delay as a function of V<sub>DD</sub>**

**Device Sizing**

© Digital Integrated Circuits<sup>2nd</sup>

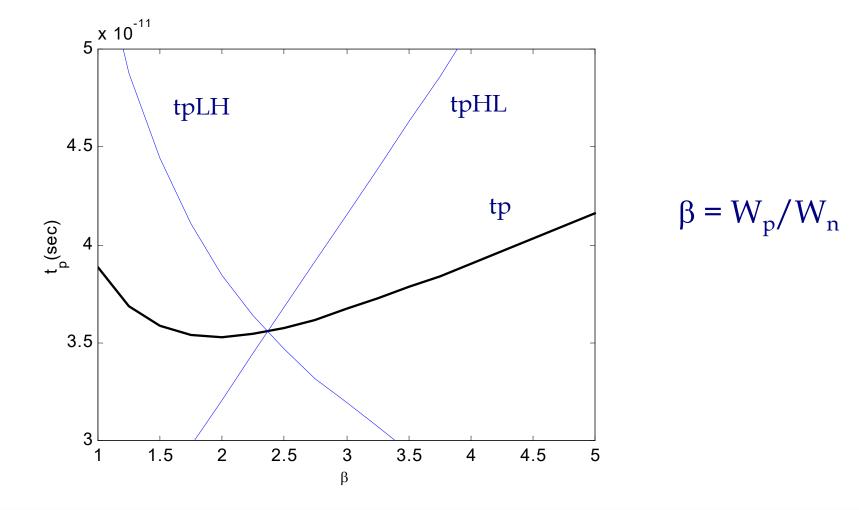

#### NMOS/PMOS ratio

#### © Digital Integrated Circuits<sup>2nd</sup>

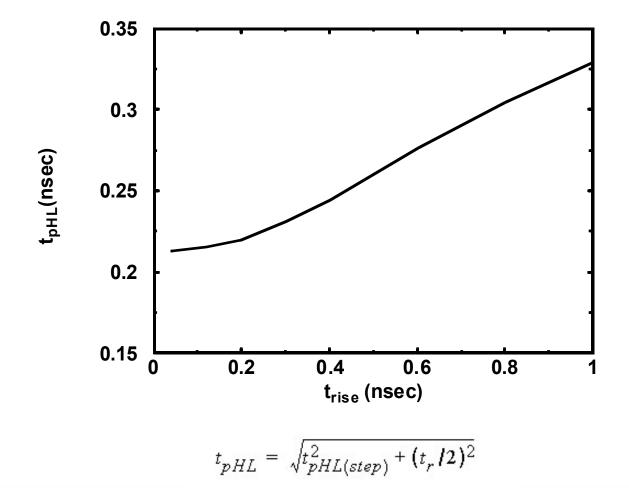

#### Impact of Rise Time on Delay

© Digital Integrated Circuits<sup>2nd</sup>