## RTL CODING AND SYNTHESIS

## For Garage Compilation

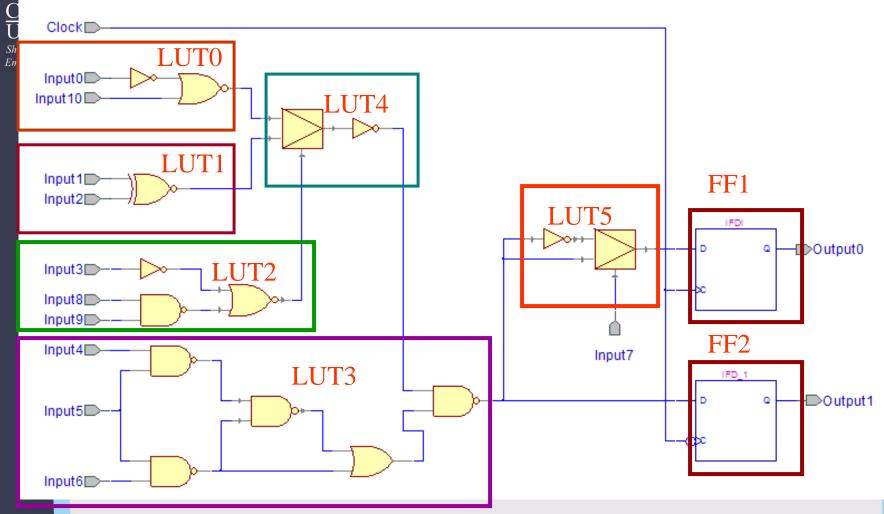

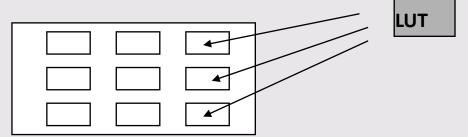

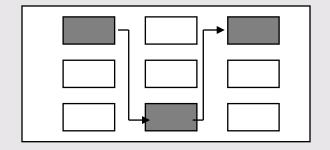

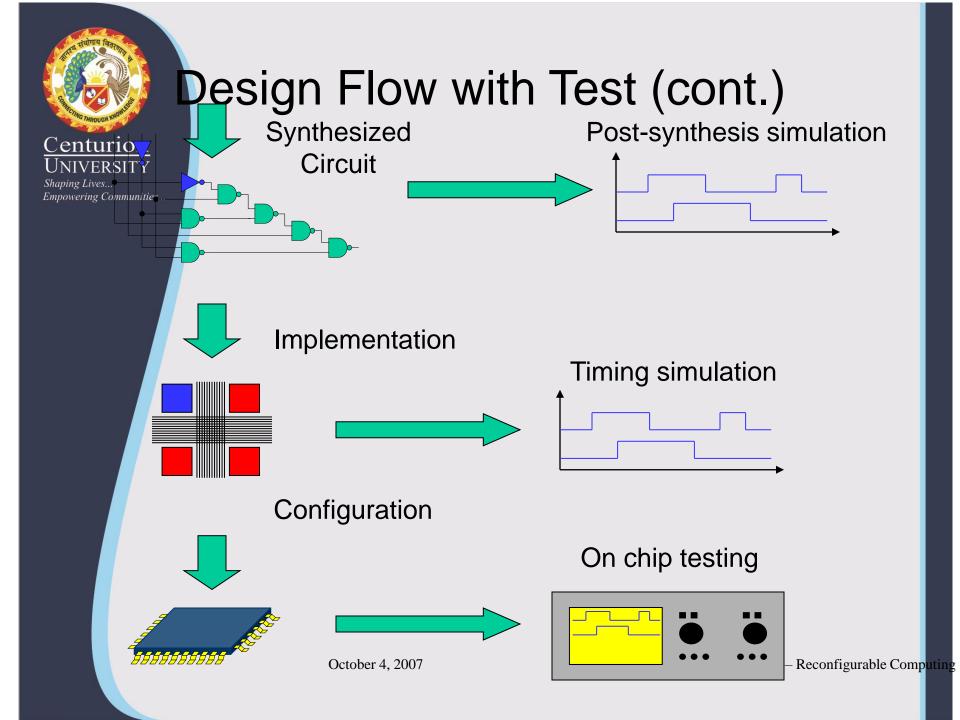

Placement

Assign a logical LUT to a physical location

Routing

Select wire segments and switches for interconnection

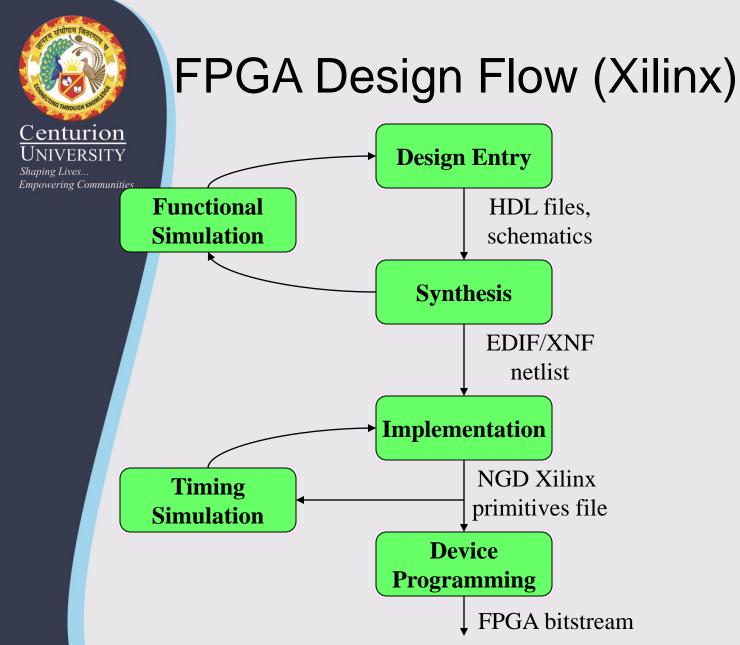

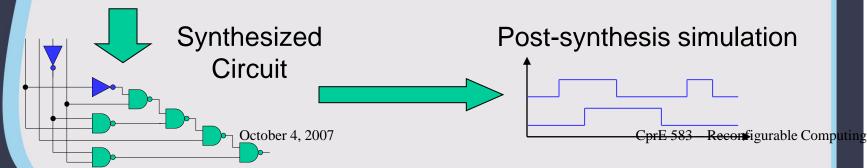

#### Design Flow with Test

p encryption with RC5-similar cipher with fixed key set The experiment 5, this

Shipping ives ur unit has to be able to perform an encryption algorithm by itself, executing 32 rounds.....

Specification

```

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity RC5 core is

clock, reset, encr_decr: in std_logic;

data_input: in std_logic_vector(31 downto 0);

data_output: out std_logic_vector(31 downto 0);

out_full: in std_logic;

key_input: in std_logic_vector(31 downto 0);

key_read: out std_logic;

end RC5 core;

```

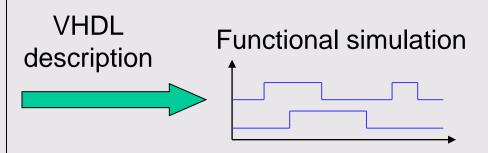

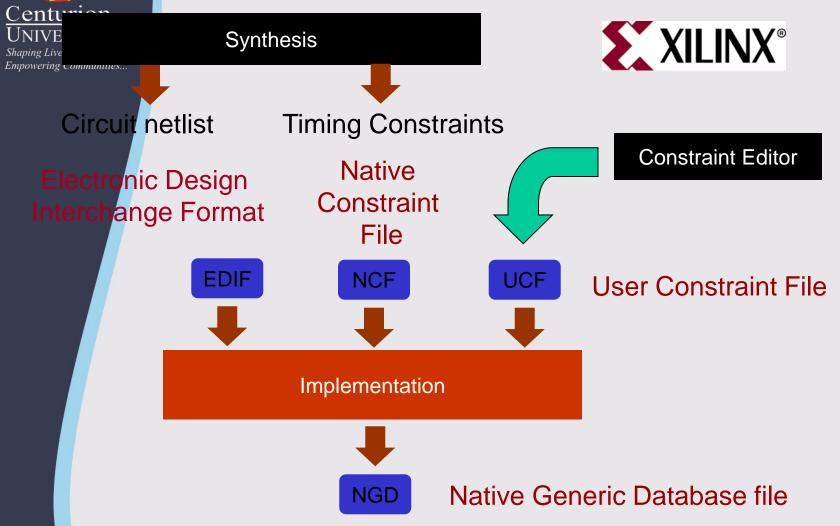

### hterpret RTL code Synthesis Tools

Sharing Lives...

Give preliminary performance estimates

Display circuit schematic corresponding to EDIF netlist

Worst slack in design: -0.924

|                   |                       | Requested<br>Clock       | Estimated Cloc |                        | Estimated                 |

|-------------------|-----------------------|--------------------------|----------------|------------------------|---------------------------|

| Starting<br>Slack | Clock Frequer<br>Type | icy Frequen<br>Grou      |                | Per:                   | iod                       |

|                   |                       |                          |                |                        |                           |

| exam1 clk         |                       | Hz 78.8 M<br>_clkgroup_0 | Hz 11.76       | 5 12.688               | -0.924                    |

| System system     | 85.0 M<br>n default_d |                          | MHz 11.76      | 65 11.572              | 2 0.193                   |

|                   |                       |                          |                | <b>EXECUTE</b> CprE 58 | 3 – Reconfigurable Comput |

# Centuria farthro

#### Implementation

October 4, 2007

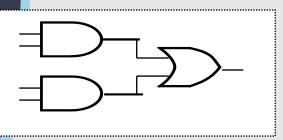

#### Circuit Netlist and Mapping